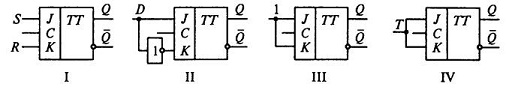

2. На рисунку наведені різні варіанти підключення входів універсального JK-тригера. Визначте, яким типам тригерів вони відповідають. |

|

| I - D-тригер, II - асинхронний T-тригер, III - синхронний T-тригер, IV - RS-тригер |

| I - RS-тригер, II - D-тригер, III - асинхронний T-тригер, IV - синхронний Т-тригер |

| I - асинхронний T-тригер, II - синхронний T-тригер, III - RS-тригер, IV - D-тригер |

| I - синхронний T-тригер, II - RS-тригер, III - D-тригер, IV - асинхронний T-тригер |