Порти введення/виведення

AVR. Програмне

введення/виведення інформації.

2 Програмне

введення/виведення даних

Опис простору І/O мікроконтролерів

AVR представлене в таблиці 1.

Таблиця 1 – Опис І/O регістрів мікроконтролера AVR2313.

|

Адрес

I/O (адрес

SRAM) |

Позна- чення |

Функція |

|

1 |

2 |

3 |

|

$3F ($5F) |

SREG |

Регістр статусу (Status Register) |

|

$3D ($5D) |

SPL |

Нижній байт показника стека (Stack Pointer Low) |

|

$3C ($5C) |

XDIV |

Регістр

керування розподілом тактової частоти (XTAL Divided Control Register) |

|

$3A ($5A) |

EICR |

Регістр керування зовнішніми перериваннями (External Interrupt Control Register) |

|

$3B ($5B) |

GIMSK |

Регістр масок зовнішніх переривань (General Interrupt Mask register) |

|

$3A ($5A) |

GIFR |

Регістр прапорів зовнішніх переривань (General Interrupt Flag Register) |

|

$39 ($59) |

TIMSK |

Регістр масок переривань

таймерів/лічильників (Tіmer/Іnterrupt Mask register) |

|

$38 ($58) |

TIFR |

Регістр прапорів переривання таймерів/лічильників (Timer/ Counter Interrupt Flag register) |

|

$35 ($55) |

MCUCR |

Регістр керування MCU (MCU General Control Register) |

|

$33 ($53) |

TCCR0 |

Регістр керування таймером/лічильником 0 (Tіmer/Counter0

Control Register) |

|

$32 ($52) |

TCNT0 |

Таймер/лічильник0 (Tіmer/Counter0 (8-bіt)) |

|

$2F ($4F) |

TCCR1A |

Керуючий регістр A таймера/лічильника 1 (Tіmer/Counter1

Control Regіster A) |

|

$2E ($4E) |

TCCR1B |

Керуючий регістр B таймера/лічильника 1 (Tіmer/Counter1

Control Regіster A) |

|

$2D ($4D) |

TCNT1H |

Старший байт таймера/лічильника 1 (Tіmer/Counter1

High Byte) |

|

$2C ($4C) |

TCNT1L |

Молодший байт таймера/лічильника 1 (Tіmer/Counter1

Low Byte) |

|

$2B ($4B) |

OCR1AH |

Старший байт регістра A порівняння виходу таймера/лічильника 1 (Tіmer/Counter1 Output Compare Regіster A High Byte) |

|

$2A ($4A) |

OCR1AL |

Молодший байт регістра A порівняння виходу таймера/ лічильника 1 (Tіmer/Counter1 Output Compare Regіster A Low Byte) |

|

$25 ($45) |

ICR1H |

Старший байт регістра захоплення таймера/лічильника 1 (Tіmer/Counter1 Input Capture Regіster Hіgh Byte) |

|

$24 ($44) |

ICR1L |

Молодший байт регістра захоплення таймера/лічильника 1 (Tіmer/Counter1 Іnput Capture Regіster Low Byte) |

|

$21 ($41) |

WDTCR |

Регістр керування сторожовим таймером (Watchdog Tіmer Control Regіster) |

|

$1E ($3E) |

EEARH |

Старший байт регістра адреси EEPROM (EEPROM Address Regіster Hіgh) |

|

$1D ($3D) |

EEDR |

Регістр даних EEPROM (EEPROM Data Regіster) |

|

$1C ($3C) |

EECR |

Регістр керування EEPROM (EEPROM Control Regіster) |

|

$18 ($38) |

PORTB |

Регістр даних порту B (Data Regіster, Port B) |

|

$17 ($37) |

DDRB |

Регістр напрямку даних порту B (Data Direction Regіster, Port B) |

|

$16 ($36) |

PINB |

Виводи входів порту B (Іnput Pins, Port B) |

Продовження

таблиці 1

|

1 |

2 |

3 |

|

$12 ($32) |

PORTD |

Регістр даних порту D (Data Regіster, Port D) |

|

$11 ($31) |

DDRD |

Регістр напрямку даних порту D (Data Dіrectіon Regіster, Port D) |

|

$10 ($30) |

PIND |

Виводи входів порту D (Іnput Pіns, Port D) |

|

$0C ($2C) |

UDR |

Регістр даних UART І/O (UART І/O Data Regіster) |

|

$0B ($2B) |

USR |

Регістр статусу UART (UART Status Regіster) |

|

$0A ($2A) |

UCR |

Регістр керування UART (UART Control Regіster) |

|

$09 ($29) |

UBRR |

Регістр керування швидкістю UART (UART Baud Rate Regіster) |

|

$08 ($28) |

ACSR |

Регістр статусу і керування аналогового компаратора (Analog Comparator Control and Status Regіster) |

Примітки: Зарезервовані

і не використовувані осередки в таблиці не показані. Усі засоби І/O і периферії

мікроконтролерів AVR

розміщені в просторі І/O. При використанні ІN і OUT використовуються

адреси регістрів І/O з $00 по $3F. Оскільки регістри І/O представлені в

адресному просторі SRAM, то до них можна адресуватися як до звичайних осередків

SRAM з адресами з $20 по $5F. Адреса SRAM виходить простим додаванням $20 до

безпосередньої адреси І/O. Адреса SRAM, по всьому документі, приведений у

круглих дужках після безпосередньої адреси І/O. Регістри І/O, у межах адрес від

$00 ($20) до $1F ($3F), побітно адресуються командами

SBІ і CBІ. Стан кожного окремого біта цих регістрів може бути перевірено

командами SBІ і SBІ.

Таблиця 2 – Простір І/O мікроконтролера

AVR2313.

|

Address |

Name |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|

$3F ($5F) |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

|

$3E ($5E) |

Reserved |

|

|||||||

|

$3D ($5D) |

SPL |

SP7 |

SP6 |

SP5 |

SP4 |

SP3 |

SP2 |

SP1 |

SP0 |

|

$3C ($5C) |

Reserved |

|

|||||||

|

$3B ($5B) |

GIMSK |

INT1 |

INT0 |

- |

- |

- |

- |

- |

- |

|

$3A ($5A) |

GIFR |

INTF1 |

INTF0 |

|

|

|

|

|

|

|

$39 ($59) |

TIMSK |

TOIE1 |

OCIE1A |

- |

- |

TICIE1 |

- |

TOIE0 |

- |

|

$38 ($58) |

TIFR |

TOV1 |

OCF1A |

- |

- |

ICF1 |

- |

TOV0 |

- |

|

$37 ($57) |

Reserved |

|

|||||||

|

$36 ($56) |

Reserved |

|

|||||||

|

$35 ($55) |

MCUCR |

- |

- |

SE |

SM |

ISC11 |

ISC10 |

ISC01 |

ISC00 |

|

$34 ($54) |

Reserved |

|

|||||||

|

$33 ($53) |

TCCR0 |

- |

- |

- |

- |

- |

CS02 |

CS01 |

CS00 |

|

$32 ($52) |

TCNT0 |

Timer/Counter0 – (8 Bit) |

|||||||

|

$31 ($51) |

Reserved |

|

|||||||

|

$30 ($50) |

Reserved |

|

|||||||

|

$2F ($4F) |

TCCR1A |

COM1A1 |

COM1A0 |

- |

- |

- |

- |

PWM11 |

PWM10 |

|

$2E ($4E) |

TCCR1B |

ICNC1 |

ICES1 |

- |

- |

CTC1 |

CS12 |

CS11 |

CS10 |

|

$2D ($4D) |

TCNT1H |

Timer/Counter1- Counter

Register High Byte |

|||||||

Продовження

таблиці 2

|

Address |

Name |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|||||||

|

$2C ($4C) |

TCNT1L |

Timer/Counter1 – Counter

Register Low Byte |

||||||||||||||

|

$2B ($4B) |

OCR1AH |

Timer/Counter1 – Compare

Register High Byte |

||||||||||||||

|

$2A ($4A) |

OCR1AL |

Timer/Counter1 – Compare

Register Low Byte |

||||||||||||||

|

$29 ($49) |

Reserved |

|

||||||||||||||

|

$28 ($48) |

Reserved |

|

||||||||||||||

|

$27 ($47) |

Reserved |

|

||||||||||||||

|

$26 ($46) |

Reserved |

|

||||||||||||||

|

$25 ($45) |

ICR1H |

Timer/Counter1 - Input

Capture Register High Byte |

||||||||||||||

|

$24 ($44) |

ICR1L |

Timer/Counter1- Input

Capture Register Low Byte |

||||||||||||||

|

$23 ($43) |

Reserved |

|

||||||||||||||

|

$22 ($42) |

Reserved |

|

||||||||||||||

|

$21 ($41) |

WDTCR |

- |

- |

- |

WDTOE |

WDE |

WDP2 |

WDP1 |

WDP0 |

|||||||

|

$20 ($40) |

Reserved |

|

||||||||||||||

|

$1F ($3F) |

Reserved |

|

||||||||||||||

|

$1E ($3E) |

EEAR |

- |

EEPROM Address Register |

|||||||||||||

|

$1D ($3D) |

EEDR |

EEPROM Data register |

||||||||||||||

|

$1C ($3C) |

EECR |

- |

- |

- |

- |

- |

EEMWE |

EEWE |

EERE |

|||||||

|

$1B ($3B) |

Reserved |

|

||||||||||||||

|

$1A ($3A) |

Reserved |

|

||||||||||||||

|

$19 ($39) |

Reserved |

|

||||||||||||||

|

$18 ($38) |

PORTB |

PORTB7 |

PORTB6 |

PORTB5 |

PORTB4 |

PORTB3 |

PORTB2 |

PORTB1 |

PORTB0 |

|||||||

|

$17 ($37) |

DDRB |

DDB7 |

DDB6 |

DDB5 |

DDB4 |

DDB3 |

DDB2 |

DDB1 |

DDB0 |

|||||||

|

$16 ($36) |

PINB |

PINB7 |

PINB6 |

PINB5 |

PINB4 |

PINB3 |

PINB2 |

PINB1 |

PINB0 |

|||||||

|

$15 ($35) |

Reserved |

|

||||||||||||||

|

$14 ($34) |

Reserved |

|

||||||||||||||

|

$13 ($33) |

Reserved |

|

||||||||||||||

|

$12 ($32) |

PORTD |

- |

PORTD6 |

PORTD5 |

PORTD4 |

PORTD3 |

PORTD2 |

PORTD1 |

PORTD0 |

|||||||

|

$11 ($31) |

DDRD |

- |

DDD6 |

DDD5 |

DDD4 |

DDD3 |

DDD2 |

DDD1 |

DDD0 |

|||||||

|

$10 ($30) |

PIND |

- |

PIND6 |

PIND5 |

PIND4 |

PIND3 |

PIND2 |

PIND1 |

PIND0 |

|||||||

|

... |

Reserved |

|

||||||||||||||

|

$0C ($2C) |

UDR |

UART I/O Data Register |

||||||||||||||

|

$0B ($2B) |

USR |

RXC |

TXC |

UDRE |

FE |

OR |

- |

- |

- |

|||||||

|

$0A ($2A) |

UCR |

RXCIE |

TXCIE |

UDRIE |

RXEN |

TXEN |

CHR9 |

RXB8 |

TXB8 |

|||||||

|

$09 ($29) |

UBRR |

UART Baud Rate Register |

||||||||||||||

|

$08 ($28) |

ACSR |

ACD |

- |

ACO |

ACI |

ACIE |

ACIC |

ACIS1 |

ACIS0 |

|||||||

|

… |

Reserved |

|

||||||||||||||

|

$00 ($20) |

Reserved |

|

||||||||||||||

2 Програмне введення/виведення даних

Програмне введення/виведення, що здійснюється за

ініціативою програми, може бути умовним та безумовним. Перший спосіб можливий

при обміні з завжди готовим зовнішнім пристроєм (ЗП), другий вимагає врахування

готовності зовнішнього пристрою до операцій введення/виведення. Алгоритм обміну

з очікуванням готовності такий, що МП може зависати в циклі очікування

готовності ЗП, причому при роботі з ЗП повільної швидкодії час очікування може

виявитись досить великим. Можливий також інший алгоритм умовного

введення/виведення, коли при неготовності ЗП МП відмовляється від операцій

обміну й продовжує основну програму. Через деякий час може бути виконана нова

спроба обміну. Втрати часу на очікування готовності виключаються при обміні за

перериванням. Зовнішні пристрої

найчастіше не мають постійної готовності до обміну та швидкісному

введення/виведення в темпі процесора.

Тому необхідно впевнитись в готовності ЗП, перше ніж почати обмін, тобто

операції введення/виведення супроводжуються спеціальними сигналами готовності,

які виробляє ЗП і вводяться до МП. Після операції введення/виведення сигнал

готовності повинен бути знятий і з’явитись при новій готовності до обміну.

Такий протокол називається квітування. Обмін відбувається зі швидкістю, яку

визначає ЗП.

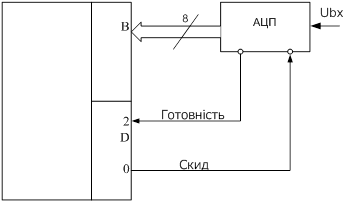

Програмне введення/виведення даних

розглянемо на прикладі організації введення даних у МП з АЦП. Спрощена схема

підключення АЦП до МП показана на рисунку 1. Обмін інформацією виконується по

шині даних через порти вводу В, D за наступним алгоритмом:

- після

завершення кожного виміру АЦП виробляє сигнал готовності даних, що через порт D

(біт D.2=0) надходить на МП;

- після

одержання сигналу готовності МП по шині даних через порт В уводить восьми

розрядний код від АЦП;

- після

закінчення прийому інформації від АЦП МП формує сигнал скидання, що надходить

на біт D0=0 шини даних і через порт виводу D передається на АЦП.

Сигнал скидання скасовує сигнал готовності АЦП і дозволяє перехід до наступного

циклу виміру;

- після видачі

сигналу скидання МП здійснює перевірку скасування сигналу готовності АЦП і у

випадку відсутності скасування сигналу готовності повторює сигнал скидання

доти, поки від АЦП не надійде сигнал "Не готовий", тобто АЦП перейде

до чергового виміру;

- після

одержання підтвердження відсутності готовності АЦП МП викликає підпрограму OBR обробки отриманих даних.

-

після закінчення підпрограми OBR МП

перевіряє, чи достатнє число результатів вимірювань отримане від АЦП. У випадку, якщо число вимірів менше

заданого N, то програма переходить до перевірки наявності сигналу готовності

АЦП, і процес вимірювань й обробки повторюється. Якщо число вимірювань у

точності дорівнює заданому числу N, то виконання програми завершується.

Рисунок 1 – Схема підключення АЦП до МК AT90S2313

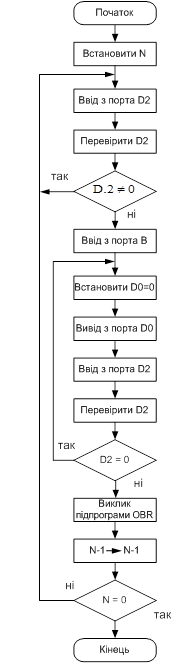

Рисунок 2 – Алгоритм введення/виведення й обробки

даних з АЦП.

|

|

LDI R22, $01 |

;Запис слова керування (D2 -

введення, D0 –

виведення) до R22 |

|

|

LDI R18, $N |

;3апис кількості чисел до R18 |

|

|

LDI R21, $00 |

;3апис слова керування до R21 для

настройки порта В на введення |

|

|

OUT $17, R21 |

;Настроїти порт В на введення

даних |

|

|

OUT $11, R22 |

; Настроїти порт D |

|

L1: |

IN R17, $10 |

;Зчитування сигналу готовності |

|

|

ANDI R17, $04 |

;Маскування сигналу готовності |

|

|

TST R17 |

;Перевірка наявності сигналу

готовності |

|

|

BRNE L1 |

;Якщо сигналу готовності немає, то

перейти до L1 |

|

|

IN R2, $16 |

;3читати дані з АЦП |

|

L2: |

CLR R3 |

;R3=0 для

формування сигналу скид |

|

|

OUT $12, R3 |

;Відправити сигнал скиду на АЦП |

|

|

IN R17, $10 |

;Зчитування сигналу готовності |

|

|

ANDI R17, $04 |

;Зчитування сигналу готовності |

|

|

TST R17 |

;Перевірка наявності сигналу

готовності |

|

|

BREQ L2 |

;Якщо сигнал готовності є, то

перейти до L2 |

|

|

RCALL OBR |

;Якщо сигналу готовності немає, то

викликається п/п OBR |

|

|

DEC R18 |

;3меньшити кількість чисел N на 1 |

|

|

TST R18 |

;Перевірка на 0 |

|

|

BRNE L1 |

;Якщо N≠0, то

перейти на L1 для зчитування нових даних з АЦП |

|

|

NOP |

;Кінець програми |

Для організації лічильника числа вимірів N

використовується регістр R18. Сигнал про готовність АЦП (нульовий логічний

рівень) водиться командою IN R17, $10 і надходить по розряду D2 до R17. За допомогою команди ANDI R17,

$04 виконується логічне множення вмісту розрядів R17 на двійковий код 0000 0100

(маскування розряду D2).

Якщо сигнал готовності АЦП відсутній (D2 = 0), то по

команді умовного переходу BRNE L1 виконання програми повторюється з мітки L1.

Організовується цикл очікування готовності АЦП. При надходженні сигналу

готовності по команді IN R2, $16 здійснюється введення даних від АЦП в R2. За допомогою команди

виводу OUT $12, R3

через порт D передається сигнал D0 = 0, що здійснює "скидання" готовності і повторний пуск АЦП.

Вивід сигналу скидання готовності циклічно повторюється доти, поки від АЦП не

надійде сигнал "не готовий" (D2 =1).

Аналого-цифровий перетворювач переходить до нового

циклу виміру, а програма звертається за допомогою оператора RCALL OBR до

підпрограми обробки результатів виміру. По завершенні підпрограми відбувається

повернення до основної програми і декрементується

зміст регістра R18. Якщо число оброблених вимірів не дорівнює N, то відбувається повернення до мітки L1 і ввід чергового результату від

АЦП. Виконання програми завершується командою

NOP, якщо число оброблених даних дорівнює N.

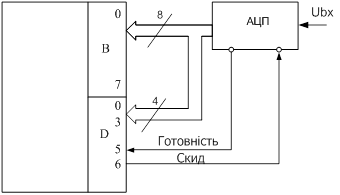

Розглянемо на прикладі програмно-кероване

введення/виведення даних, коли один і той же порт використовується як для

введення, так і для виведення. Необхідно вивести 20 даних з ОЗП з адресою $60

на ЦАП (спочатку формується сигнал скиду – 0, перевіряється наявність сигналу

готовності – 1, виводяться дані), прочитати дані з АЦП (перевірити сигнал

готовності – 1, зчитати дані з АЦП, сформувати сигнал скиду – 0), записати

зчитані дані в ОЗП за адресою, починаючи з $60.

Рисунок 3 –

Схема підключення АЦП, ЦАП до МК AT90S2313

|

|

LDI R20, 20d |

;Запис до R20 кількості

чисел |

|

|

CLR R31 |

;Ініціалізація

регістрової пари Z і запис до R31 числа

$00 |

|

|

LDI R30, $60 |

;Ініціалізація

Z і запис до R30 числа $60

(адресу першого числа) |

|

M1: |

LPM |

;Зчитування

першого числа до R0 |

|

|

SER R9 |

;Установка

в R9 всіх біт

для настройки порта В на виведення даних |

|

|

OUT $17, R9 |

;Порт В

настроєний |

|

|

LDI R25, $81 |

;Установка

керуючого слова для порта D (D7 = 1, D4 = 0, D2 = 1, ; D0 = 0) |

|

|

LDI R16, $01 |

;Установка

слова керування для пуска ЦАП (D0 = 0, щоб не ;запустити

АЦП) |

|

|

OUT $11, R25 |

;Порт D

настроєний на роботу (D7 – out, D4 – in, D2 – out, D0 – in) |

|

|

OUT $12, R16 |

;Пуск ЦАП |

|

L1: |

SBIS $10, 4 |

;Перевірка

наявності сигналу готовності ЦАП |

|

|

RJMP L1 |

;Очікування

сигналу готовності ЦАП |

|

|

OUT $18, R0 |

;Відправка

даних на ЦАП з R0 |

|

|

CLR R9 |

;Скидання

усіх біт в R9 для настройки порта В на ввід |

|

|

OUT $17, R9 |

;Порт В

настроєний на введення данних |

|

L2: |

SBIS $10,

2 |

;Перевірка

сигналу готовності від АЦП |

|

|

RJMP L2 |

;Очікування

сигналу готовності ЦАП |

|

|

IN R0, $16 |

;3читування

даних з АЦП |

|

|

LDI R16, $80 |

;Установка

слова керування для пуска АЦП(D7 = 0, щоб не ;запустити

ЦАП) |

|

|

OUT $12, R16 |

;Скид АЦП |

|

|

SPM |

;3апис

зчитаного числа з АЦП до ОЗП, адреса якої в Z |

|

|

INC R30 |

3більшення

адреси комірки ОЗП на 1 |

|

|

DEC R10 |

;3меньшити

кількість чисел N на 1 |

|

|

TST R10 |

;Перевірка

на 0 |

|

|

BRNE Ml |

;Якщо N¹0, то

перейти на L1 для зчитування нових даних з АЦП |

|

|

NOP |

;Кінець

програми |

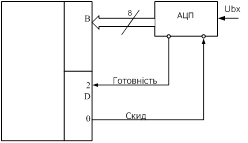

Задача 1. Зчитати 20 чисел з 12 розрядного АЦП. Результат зберегти в комірках

пам’яті починаючи з адреси 80h.

Розробити функціональну схему та написати

програму на мові Асемблер.

Рисунок 4

– Функціональна схема програмно-керованого обміну між мікроконтролером

та АЦП

Обмін інформацією виконується по шині даних через

порти вводу В, D за

наступним алгоритмом:

-

після завершення кожного виміру АЦП виробляє сигнал

готовності даних, що через порт D (біт D.5=0)

надходить на МП;

-

після одержання сигналу готовності МП по шині даних

через порт В уводить восьмирозрядний код та по шині

даних через порт D чотирьохрозрядний

код від АЦП;

-

після закінчення прийому інформації від АЦП МП формує

сигнал скидання, що надходить на біт D6=0 шини даних і через порт виводу D

передається на АЦП. Сигнал скидання скасовує сигнал готовності АЦП і дозволяє

перехід до наступного циклу виміру;

-

після видачі сигналу скидання МП здійснює перевірку

скасування сигналу готовності АЦП і у випадку відсутності скасування сигналу

готовності повторює сигнал скидання доти, поки від АЦП не надійде сигнал «Не

готовий», тобто АЦП перейде до чергового виміру;

-

після одержання підтвердження відсутності готовності

АЦП МП викликає підпрограму OBR обробки отриманих даних.

-

після закінчення підпрограми OBR МП перевіряє, чи

достатнє число результатів вимірювань отримане від АЦП. У випадку, якщо число вимірів менше заданого N, то програма

переходить до перевірки наявності сигналу готовності АЦП, і процес вимірювань й

обробки повторюється. Якщо число вимірювань у точності дорівнює заданому числу N, то

виконання програми завершується.

|

|

CLR R27 |

; |

|

|

LDI R26, $80 |

;

налаштування регістрової пари Х |

|

|

LDI

R22, RamEnd |

; |

|

|

OUT

SPL, R22 |

; налаштування

стеку |

|

|

LDI

R22, $40 |

;запис слова

керування (D5-D0

– введення, D6 – виведення) |

|

|

LDI

R18, 20 |

;запис

кількості чисел до R18 |

|

|

LDI

R21, $00 |

;запис слова

керування до R21 для

настройки порта В на ;введення |

|

|

OUT

$17, R21 |

;настроїти

порт В на введення даних |

|

|

OUT

$11, R22 |

;настроїти

порт D |

|

L1: |

IN

R17, $10 |

;зчитування

сигналу готовності |

|

|

ANDI

R17, $20 |

;маскування

сигналу готовності |

|

|

TST

R17 |

;перевірка

наявності сигналу готовності |

|

|

BRNE

L1 |

;якщо сигналу

готовності немає, то перейти до L1 |

|

|

IN

R2, $16 |

;зчитати дані

з АЦП (молодших 8 біт) |

|

|

IN

R20, $10 |

;зчитати дані

з АЦП (старших 4 біт) ;виділення

старших 4 біт |

|

|

ANDI

R20, $0F |

|

|

L2: |

CBI $12,6 |

;відправити

сигнал скиду на АЦП |

|

|

IN

R17, $10 |

;зчитування

сигналу готовності |

|

|

ANDI R17, $20 |

;зчитування

сигналу готовності |

|

|

TST R17 |

;перевірка

наявності сигналу готовності |

|

|

BREQ

L2 |

;якщо сигнал

готовності є, то перейти до L2 |

|

|

RCALL

OBR |

;якщо сигналу

готовності немає, то викликається п/п OBR |

|

|

SBI $12, 6 |

;зняти сигнал

скиду АЦП |

|

|

DEC

R18 |

;зменшити

кількість чисел N на 1 |

|

|

TST

R18 |

;перевірка на

0 |

|

|

BRNE

L1 |

;якщо N≠0, то перейти на L1 для

зчитування нових даних |

|

|

NOP |

;Кінець

програми |

|

|

|

|

|

OBR: |

ST X+, R2 |

; підпрограма

запису чисел до комірок пам’яті |

|

|

ST X+, R20 |

|

|

|

RET |

Задача 2. Зчитати 30 чисел з 8 розрядного АЦП, всі числа що перевищують 100

переписати в комірки пам’яті SRAM починаючи з $60, всі числа що менше 10 переписати в комірки пам’яті SRAM починаючи з

$А0. Додати всі числа, результат зберегти в R8.

Рисунок 5

– Функціональна схема програмно-керованого обміну між мікроконтролером

та АЦП

Обмін інформацією виконується по шині даних через

порти вводу В, D за

наступним алгоритмом:

-

після завершення кожного виміру АЦП виробляє сигнал

готовності даних, що через порт D (біт D.2=0)

надходить на МП;

-

після одержання сигналу готовності МП по шині даних

через порт В уводить восьмирозрядний код від АЦП;

-

після закінчення прийому інформації від АЦП МП формує

сигнал скидання, що надходить на біт D.0=0 шини даних і через порт виводу

D передається на АЦП. Сигнал скидання скасовує сигнал готовності АЦП і дозволяє

перехід до наступного циклу виміру;

-

після видачі сигналу скидання МП здійснює перевірку

скасування сигналу готовності АЦП і у випадку відсутності скасування сигналу

готовності повторює сигнал скидання доти, поки від АЦП не надійде сигнал «Не

готовий», тобто АЦП перейде до чергового виміру;

-

після одержання підтвердження відсутності готовності

АЦП МП викликає підпрограму OBR обробки отриманих даних.

-

після закінчення підпрограми OBR МП перевіряє, чи

достатнє число результатів вимірювань отримане від АЦП. У випадку, якщо число вимірів менше заданого N, то програма

переходить до перевірки наявності сигналу готовності АЦП, і процес вимірювань й

обробки повторюється. Якщо число вимірювань у точності дорівнює заданому числу N, то

виконання програми завершується.

|

|

CLR R27 |

; |

|

|

LDI R26, $60 |

;

налаштування регістрової пари Х |

|

|

CLR R29 |

; |

|

|

LDI R28, $A0 |

;

налаштування регістрової пари Y |

|

|

CLR R8 |

; очищення

регістру, де зберігається результат |

|

|

LDI

R22, RamEnd |

; |

|

|

OUT

SPL, R22 |

; налаштування

стеку |

|

|

LDI

R22, $01 |

;запис слова

керування (D2 - введення, D0

– ;виведення) до

R22 |

|

|

LDI

R18, 30 |

;запис

кількості чисел до R18 |

|

|

LDI

R21, $00 |

;запис слова

керування до R21 для

настройки ;порта В на введення |

|

|

OUT

$17, R21 |

;настроїти

порт В на введення даних |

|

|

OUT

$11, R22 |

;настроїти

порт D |

|

L1: |

IN

R17, $10 |

;зчитування

сигналу готовності |

|

|

ANDI

R17, $04 |

;маскування

сигналу готовності |

|

|

TST

R17 |

;перевірка

наявності сигналу готовності |

|

|

BRNE

L1 |

;якщо сигналу

готовності немає, то перейти до L1 |

|

|

IN

R2, $16 |

;зчитати дані

з АЦП |

|

L2: |

CLR

R3 |

;R3=0 для формування сигналу скид |

|

|

OUT

$12, R3 |

;відправити

сигнал скиду на АЦП |

|

|

IN

R17, $10 |

;зчитування

сигналу готовності |

|

|

ANDI R17, $04 |

;зчитування

сигналу готовності |

|

|

TST R17 |

;перевірка

наявності сигналу готовності |

|

|

BREQ

L2 |

;якщо сигнал

готовності є, то перейти до L2 |

|

|

RCALL

OBR |

;якщо сигналу

готовності немає, то викликається ;підпрограма OBR |

|

|

DEC

R18 |

;зменшити

кількість чисел N на 1 |

|

|

TST

R18 |

;перевірка на

0 |

|

|

BRNE

L1 |

;якщо N≠0, то перейти на L1 для

зчитування нових ;даних з АЦП |

|

|

NOP |

;кінець

програми |

|

|

|

|

|

OBR: |

MOV R20, R2 |

|

|

|

CPI R20, 101 |

|

|

|

BRSH K1 |

|

|

|

CPI R20, 10 |

|

|

|

BRLO K2 |

|

|

|

ADC R8, R2 |

|

|

K3: |

RET |

|

|

K1: |

ST X+, R2 |

|

|

|

RJMP K3 |

|

|

K2: |

ST Y+, R2 |

|

|

|

RJMP K3 |

|