Архітектура

мікроконтролерів з CISC архітектурою

1 Структурна організація мікроконтролера i8051

2 Організація ОЗП, ПЗП і регістрів мікроконтролера 8051

3 Організація портів введення/виведення

мікроконтролера 8051

4 Таймери / лічильники мікроконтролерів сімейства 8051

5 Послідовний порт мікроконтролера

6 Система переривань мікроконтролера 8051

У даний час серед усіх 8-розрядних мікроконтролерів - сімейство MCS-51 є безсумнівним

чемпіоном з кількості різновидів і кількості компаній, що випускають його

модифікації. Воно одержало свою назву від першого представника цього сімейства

- мікроконтролера 8051, випущеного в 1980 році на

базі технології HMOS. Вдалий набір периферійних пристроїв, можливість гнучкого

вибору зовнішньої чи внутрішньої програмної пам'яті і прийнятна ціна

забезпечили цьому мікроконтролеру успіх на ринку. З

погляду технології мікроконтролер 8051 був для свого

часу дуже складним виробом - у кристалі було використано 128 тис. транзисторів,

що в 4 рази перевищувало кількість транзисторів у 16-розрядному мікропроцесорі

8086.

На сьогоднішній день існує більш

200 модифікацій мікроконтролерів сімейства 8051, що

випускаються майже 20-ю компаніями. Щороку з'являються всі нові варіанти

представників цього сімейства. Основними напрямками розвитку є: збільшення

швидкодії (підвищення тактової частоти і переробка архітектури), зниження

напруги живлення і споживання, збільшення обсягу ОЗП і FLASH..

Усі мікроконтролери

із сімейства MCS-51 мають загальну систему команд. Наявність додаткових

пристроїв впливає тільки на кількість регістрів спеціального призначення. Основними

виробниками клонів 51-го сімейства у світі є фірми Philips,

Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond,

Silicon Systems і ряд

інших.

У рамках СРСР виробництво мікроконтролера 8051 здійснювалося в Києві, Воронежі

(1816ВЕ31/51, 1830ВЕ31/51), Мінську (1834ВЕ31) і Новосибірську (1850ВЕ31).

1 Структурна організація мікроконтролера i8051

Мікроконтролери сімейства

8051 мають такі апаратні особливості:

- внутрішнє

ОЗП обсягом 128 байт;

- чотири

двонаправлених 8-разрядних портів введення/виведення,

що побітно настроюються;

- два

16-розрядних таймери-лічильники;

- вбудований

тактовий генератор;

- адресація

64 Кбайт пам'яті програм і 64 Кбайт

пам'яті даних;

- дві

лінії запитів на переривання від зовнішніх пристроїв;

- інтерфейс

для послідовного обміну інформацією з іншими мікроконтролерами

або персональними комп'ютерами.

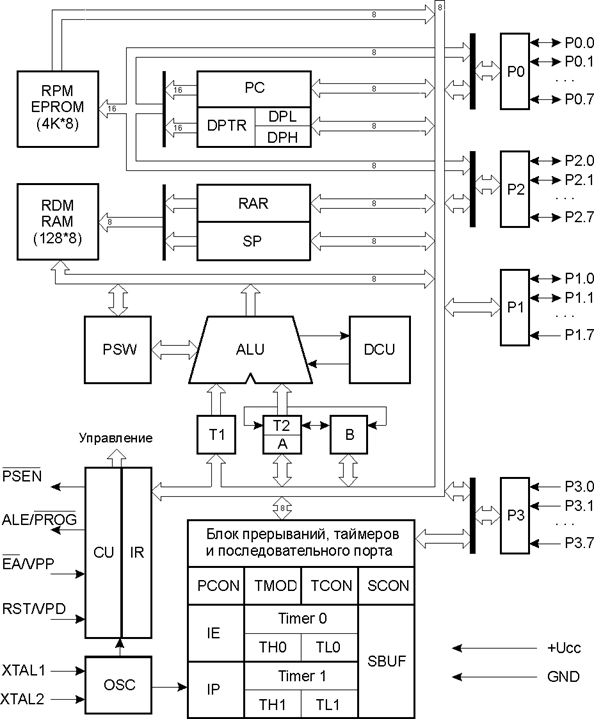

Рисунок 1 – Структурна схема мікроконтролера

КМ1816ВЕ51

Функціональна

схема мікроконтролера сімейства 8051 наведена на

рисунку 1, а на рисунку 2 показано

призначення виводів. Мікроконтролер виконано на

основі високорівневої n-МОП технології. Через

чотири програмованих паралельних порти введення/виведення й один послідовний

порт мікроконтролер взаємодіє з зовнішніми пристроями.

Основу схеми (рис. 1) утворює внутрішня двохнаправлена

8-бітна шина, що зв'язує між собою основні вузли і пристрої мікроконтролера:

резидентна пам'ять програм (RPM), резидентна пам'ять даних (RDM),

арифметико-логічний пристрій (ALU), блок регістрів спеціальних функцій,

пристрій керування (CU) і порти введення/виведення (P0-P3).

8-бітний арифметико-логічний пристрій

(ALU) може виконувати арифметичні операції додавання, віднімання, множення і

ділення; логічні операції І, АБО, виключне АБО, а також операції циклічного

зрушення, скидання, інвертування і т.п. До входів підключені

програмно-недоступні регістри T1 і T2, призначені для тимчасового збереження операндів, схема десяткової корекції (DCU) і схема

формування ознак результату операції (PSW).

Рисунок 2 –

Призначення виводів 8051

Позначення виводів:

-

VSS — потенціал загального проводу

("землі");

-

VCC — основна напруга літанія +5 В;

-

X1, X2 — виводи для підключення кварцового резонатора;

-

RST — вхід загального скидання мікроконтролера;

-

PSEN — дозвіл зовнішньої пам'яті програм; видається тільки

при звертанні до зовнішнього ПЗП;

-

ALE — строб адреси зовнішньої пам'яті;

-

ЕА — відключення внутрішньої програмної пам'ять; рівень 0 на

цьому вході змушує мікроконтролер виконувати програму

тільки зовнішнього ПЗП;

-

P1 — восьмибітний квазідвонаправлений порт введення/виведення: кожен розряд

порту може бути запрограмований як на введення, так і на виведення інформації,

незалежно від стану інших розрядів;

-

P2 — восьмибітний квазідвонаправлений порт, аналогічний Р1; крім того, виводи

цього порту використовуються для видачі адресної інформації при звертанні до

зовнішньої пам'яті чи програм даних (якщо використовується 16-бітова адресація

останньої).

-

Р3 — восьмибітний квазідвонаправлений порт, аналогічний Р1; крім того, виводи

цього порту можуть виконувати ряд альтернативних функцій, що використовуються

при роботі таймерів, порту послідовного введення/виведення, контролера

переривань, і зовнішньої пам'яті програм і даних;

-

P0 — восьмибітний двонаправлений порт вводу-вивоку

інформації: при роботі з зовнішніми ОЗП і ПЗП по лініях порту в режимі

тимчасового мультиплексування видається адреса зовнішньої пам'яті, після чого

здійснюється чи передача прийом даних.

2 Організація ОЗП, ПЗП і регістрів мікроконтролера 8051

Пам'ять програм (ПЗП)

Як і в більшості мікроконтролерів, у мікроконтролерів

сімейства 8051, пам'ять програм і пам'ять даних є самостійними і незалежними

одне від одного пристроями, адреованими різними

командами і керуючими сигналами.

Обсяг вбудованої пам'яті програм,

розташованої на кристалі мікроконтролера 8051дорівнює

4 Кбайт. При звертанні до зовнішньої пам'яті програм

усі мікроконтролери сімейства 8051 завжди

використовують 16-розрядну адресу, що забезпечує їм доступ до 64 Кбайт ПЗП. Мікроконтролер

звертається до програмної пам'яті при читанні коду операції й операндів (використовуючи лічильник команд PC), а також при

виконанні команд переносу байта з пам'яті програм в акумулятор. При виконанні

команд перенесення даних адресація комірки пам'яті програм, з якої будуть

прочитані дані, може здійснюватися з використанням як лічильника PC, так і

спеціального двобайтового регістра-покажчика даних

DPTR.

Пам'ять даних (ОЗП)

Обсяг розташованої на кристалі

пам'яті даних—128 байт. Обсяг зовнішньої пам'яті даних може досягати 64 Кбайт. Перші 32 байта організовані в чотири банки регістрів

загального призначення, що позначаються відповідно банк 0 — банк 3. Кожний з

них складається з восьми регістрів R0 — R7. У будь-який момент програмі

доступний тільки один банк регістрів, номер якого міститься в третьому і

четвертому бітах слова стану програми PSW.

Адресний простір, що залишився,

може конфігуруватися розроблювачем за своїм розсудом: у ньому розташовуються

стек, системні і користувацькі області даних. Звертання до комірок пам'яті

даних можливо двома способами. Перший спосіб — пряма адресація комірки пам'яті.

У цьому випадку адреса осередку є операндом

відповідної команди. Другий спосіб — непряма адресація за допомогою регістрів

R0 або R1: перед виконанням відповідної команди в один з них повинна бути

занесена адреса комірки, до якої необхідно звернутися.

Для звертання до зовнішньої пам'яті

даних використовується тільки непряма адресація за допомогою регістрів R0 і R1

або за допомогою 16-розрядного регістра-покажчика DPTR. Він відноситься до

групи регістрів спеціальних функцій, і з його допомогою можна адресувати всі 64

Кбайти зовнішньої пам'яті.

Частина пам'яті даних являє собою

так звану бітову область, у ній мається можливість за допомогою спеціальних

бітових команд адресуватися до кожного розряду комірок пам'яті. Адреса прямо

адресованих бітів може бути записана або у виді (Адреса Байта ).(Розряд),

наприклад, вираз 21.3 означає третій розряд комірки пам'яті з адресою 21H, або

у виді абсолютної бітової адреси. Відповідність цих двох способів адресації

можна визначити за таблицею 1.

Таблиця

1 – Адреси бітових областей пам'яті мікроконтролера

8051

|

Адреса байта |

Адреси біт по розрядах |

|||||||

|

Adr |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

2FH |

7F |

7E |

7D |

7C |

7B |

7A |

79 |

78 |

|

2EH |

77 |

76 |

75 |

74 |

73 |

72 |

71 |

70 |

|

2DH |

6F |

6E |

6D |

6C |

6B |

6A |

69 |

68 |

|

2CH |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 |

|

2BH |

5F |

5E |

5D |

5C |

5B |

5A |

59 |

58 |

|

2AH |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 |

|

29H |

4F |

4E |

4D |

4C |

4B |

4A |

49 |

48 |

|

28H |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

|

27H |

3F |

3E |

3D |

3C |

3B |

3A |

39 |

38 |

|

26H |

37 |

36 |

35 |

34 |

33 |

32 |

31 |

30 |

|

25H |

2F |

2E |

2D |

2C |

2B |

2A |

29 |

28 |

|

24H |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

|

23H |

1F |

1E |

1D |

1C |

1B |

1A |

19 |

18 |

|

22H |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

|

21H |

0F |

0E |

0D |

0C |

0B |

0A |

09 |

08 |

|

20H |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

Регістри спеціальних

функцій

До адресного простору пам'яті даних

примикає адресний простір регістрів спеціальних функцій SFR (Special Function Register). Адреси, по яких розташовані ці регістри,

наведені в таблиці 2.

Таблиця 2 – Розміщення регістрів спеціальних функцій у

просторі SFR

|

Адреса |

Символ |

Найменування

|

|

0E0H |

АСС |

Акумулятор (Accumulator) |

|

0F0H |

В |

Регістр розширювач акумулятора (Multiplication

Register) |

|

0D0H |

PSW |

Слово стану програми (Program Status Word) |

|

080Н |

P0 |

Порт 0 (SFR P0) |

|

090H |

Р1 |

Порт 1 (SFR P1) |

|

0A0H |

P2 |

Порт 2

(SFR P2) |

|

0B0H |

P3 |

Порт 3

(SFR РЗ) |

|

081H |

SP |

Регістр-вказівник стека (Stack

Pointer) |

|

083H |

DPH |

Старший байт регістра-вказівника даних DPTR

(Data Pointer High) |

|

082H |

DPL |

Молодший байт регістра-вказівника даних

DPTR (Data Pointer Low) |

|

08CH |

TH0 |

Старший байт таймера 0 () |

|

08AH |

TL0 |

Молодший байт таймера 0 () |

|

08DH |

TH1 |

Старший байт таймера 1 () |

|

08BH |

TL1 |

Молодший байт таймера 1 () |

|

089H |

TMOD |

Регістр режимів таймерів-лічильників (Timer/Counter Mode Control

Register) |

|

088H |

TCON |

Регістр керування-статуса таймерів (Timer/Counter Control

Register) |

|

0B8H |

IP |

Регістр пріоритетів (Interrupt Priority Control Register) |

|

0A8H |

IE |

Регістр маски переривання (Interrupt Enable Register) |

|

087H |

PCON |

Регістр керування живленням (Power Control Register) |

|

098H |

SCON |

Регістр керування прийомопередавачем

(Serial Port Control Register) |

|

099H |

SBUF |

Буфер прийомопередавачем (Serial Data Buffer) |

Відзначимо, що регістри займають

тільки частину 128-байтового адресного простору. Ті комірки пам'яті з адресами

80H-0FFH, що не зайняті регістрами, фізично відсутні, на кристалах мікроконтролерів сімейства 8051 при звертанні до них можна

прочитати лише код команди повернення.

Регістри спеціальних функцій

керують роботою блоків, що входять у мікроконтролер:

-

регістр SFR паралельних портів P0...P3 - служать для

введення-виведення інформації;

-

дві регістрові пари з іменами TH0, TL0 і TH1, TL1 являють

собою регістри, двох програмно-керованих 16-бітних таймерів-лічильників;

-

режими таймерів-лічильників задаються з використанням

регістра TMOD, а керування ними здійснюється за допомогою регістра TCON;

-

для керування режимами енергоспоживання використовується

регістр PCON;

-

регістри IP і IE керують роботою системи переривань;

-

регістри SBUF і SCON — роботою прийомопередавача

послідовного порту;

-

регістр-покажчик стека SP – восьмибітний.

Він може адресувати будь-яку область внутрішньої пам'яті даних. У процесі

ініціалізації мікроконтролера після сигналу скидання або

при включенні напруги живлення в SP заноситься код 07Н. Це означає, що перший

елемент стека буде розташовуватися в комірці пам'яті з адресою 08Н;

-

регістр-покажчик даних DPTR найчастіше використовують для

фіксації 16-бітної адреси в операціях звертання до зовнішньої пам'яті програм і

даних. Він може використовуватись як один 16-бітний регістр, так і як два

незалежних регістри DPL і DPH;

-

акумулятор (АСС) є джерелом операнда

і місцем фіксації результату при виконанні арифметичних, логічних операцій і

ряду операцій передачі даних. У розпорядженні користувача маються 8 регістрів

загального призначення R0–R7 одного з чотирьох можливих банків. При виконанні

багатьох команд в АЛП формується ряд ознак операції (прапорів), що фіксуються в

регістрі PSW;

-

регістр В використовується при операціях множення і ділення. Звертання до нього, як і до регістра

SFR, виконується аналогічно акумулятору;

-

при виконанні ряду команд в арифметико-логічному пристрої

(АЛП) формуються ознаки операцій, що фіксуються в регістрі PSW (таблиця 3).

Таблиця 3 –

Перелік прапорів, їхні символічні імена й умови формування

|

Символ |

Позиція |

Ім'я і призначення |

||||||||||||||||||||

|

P |

PSW.0 |

Прапор пріоритету.

Встановлюється і скидається апаратно в кожнім циклі команди і фіксує

непарне/парне число одиничних біт в акумуляторі |

||||||||||||||||||||

|

- |

PSW.1 |

Не

використовується |

||||||||||||||||||||

|

OV |

PSW.2 |

Прапор

переповнення. Встановлюється і скидається апаратно при виконанні арифметичних

операцій |

||||||||||||||||||||

|

RS0 - RS1 |

PSW.3 - PSW.4 |

Біти вибору

використовуваного банку регістрів. Можуть бути змінені програмними шляхом

|

||||||||||||||||||||

|

F0 |

PSW.5 |

Прапор

користувача. Може бути встановлений, скинутий чи перевірений програмою

користувача |

||||||||||||||||||||

|

АС |

PSW.6 |

Прапор допоміжного

переносу. Встановлюється і скидається тільки апаратними засобами при

виконанні команд додавання і вирахування і сигналізує про чи запозичення в

біті 3 акумулятори |

||||||||||||||||||||

|

C |

PSW.7 |

Прапор переносу.

Встановлюється і скидається як апаратно, так і програмним шляхом |

Найбільше “активним” прапором PSW є прапор переносу, що

бере участь і модифікується в процесі виконання багатьох операцій, включаючи

додавання, віднімання і зсуву. Крім того, прапор переносу (C) виконує функції “булева акумулятора” у командах, що маніпулюють з бітами.

Прапор переповнення (OV) фіксує арифметичне переповнення при операціях над

цілими числами зі знаком і уможливлює використання арифметики в додаткових

кодах. ALU не керує прапорами селекції банку регістрів (RS0, RS1), їхнє

значення цілком визначається прикладною програмою і використовується для вибору

одного з чотирьох регістрових банків.

У Intel

8051 є акумулятор але велику кількість команд

можна виконувати без його участі. Наприклад, дані можуть бути передані з

будь-якого осередку RDM у будь-який регістр, будь-який регістр може бути

завантажений безпосереднім операндом і т.д.

3 Організація портів введення/виведення мікроконтролера 8051

Кількість портів –

4. Назва – P0...P3, вони адресуються як

регістри спеціальних функцій. Розрядність - 8 з можливістю адресації розрядів побітно. Усі порти двохнаправлені,

причому мається можливість у кожному порту частина розрядів використовувати для

введення даних, а частина для виведення.

Через обмежену кількість виводів

корпуса ІМС мікроконтролера, більшість виводів

використовується для виконання функцій лінії порту і для альтернативних функцій:

- порти P0 і Р2 використовуються при звертанні до зовнішньої пам'яті.

При цьому на виходах P0 молодший байт адреси зовнішньої пам'яті мультиплексується з байтом, що вводиться/виводиться.

Виходи Р2 містять старший байт адреси зовнішньої пам'яті, якщо адреса

16-розрядна. При використанні восьмиразрядної

адреси портом Р2 можна користатися для введення/виведення інформації

звичайним образом. При звертанні до зовнішньої пам'яті в P0 автоматично

заносяться 1 в усі біти. Інформація в Р2 при цьому залишається незмінною;

- порт P3 крім звичайного

введення і виведення інформації використовується для формування і прийому

спеціальних керуючих і інформаційних сигналів.

Альтернативні

функції можуть бути активовані тільки в тому випадку, якщо у відповідні біти

порту P3 попередньо занесені 1. Невикористані альтернативним способом розряди

можуть працювати як звичайно.

Таблиця 4 – Альтернативні

функції портів мікроконтролера

|

Вивід

порту |

Альтернативна

функція |

|

Р3.0 |

RXD - вхід послідовного порту |

|

Р3.1 |

TXD - вихід послідовного порту |

|

Р3.2 |

INT0 - зовнішнє переривання 0 |

|

Р3.3 |

INT1 - зовнішнє переривання 1 |

|

Р3.4 |

Т0 - вхід таймера-лічильника 0 |

|

Р3.5 |

Т1 - вхід таймера-лічильника 1 |

|

Р3.6 |

WR - строб запису в

зовнішню пам'ять даних |

|

Р3.7 |

RD - строб читання з зовнішньої пам'яті даних |

4 Таймери / лічильники мікроконтролерів сімейства 8051

У базових моделях сімейства маються

два програмовних 16-бітних таймери/лічильника (T/C0 і

T/C1), що можуть бути використані як таймери, так і як лічильники зовнішніх

подій. У першому випадку вміст відповідного таймера/лічильника (Т/С) інкрементуєтся в кожномумашинному

циклі, тобто через кожні 12 періодів коливань кварцового резонатора, у другому

вони інкрементуются під впливом переходу з 1 у 0

зовнішнього вхідного сигналу, поданого на відповідний вхід T0 або T1. Оскільки

на розпізнавання періоду вимагаються два машинних цикли, максимальна частота

підрахунку вхідних сигналів дорівнює 1/24 частоти резонатора. На тривалість

періоду вхідних сигналів обмежень зверху немає. Для гарантованого читання

вхідний сигнал повинний утримувати значення 1, як мінімум, протягом одного

машинного циклу. Для керування режимами роботи Т/С та для організації їхньої

взаємодії із системою переривань використовуються два регістри спеціальних

функцій (TMOD і TCON), опис яких наведений у таблиці 5 та 6.

Таблиця 5 – Регістр режиму роботи таймера/лічильника TMOD

|

Символ |

Позиція |

Ім’я

та призначення |

|

1 |

2 |

3 |

|

GATE |

TMOD.7 для Т/С1 і

TMOD.3 для Т/СО |

Керування блокуванням. Якщо біт встановлений, то

таймер/лічильник "x" дозволений доти, поки на вході "lNTx" високий рівень і біт керування "TRx" установлений. Якщо біт скинутий, то Т/С

дозволяється, як тільки біт керування "TRx"

установлюється |

|

С/Т |

TMOD.6 для T/C1 і

TMOD.2 для Т/СО |

Біт

вибору режиму чи таймера лічильника подій. Якщо біт скинутий, то

працює таймер від внутрішнього джерела сигналів синхронізації. Якщо;

установлений, то працює лічильник від зовнішніх сигналів на вході "Tx" |

Продовження таблиці 5

|

1 |

2 |

3 |

|||||||||||||||

|

M1 |

TMOD.5 для T/C1 і

TMOD.1 для Т/СО |

Режим роботи

|

|||||||||||||||

|

M0 |

TMOD.4 для Т/С1 і TMOD.0

для Т/СО |

Таблиця 6 – Регістр

керування/статусу таймера TCON

|

Символ |

Позиція |

Ім'я і призначення |

|

TF1 |

TCON.7 |

Прапор переповнення таймера 1. Встановлюється

апаратно при переповненні таймера/лічильника. Скидається при обслуговуванні

переривання апаратно |

|

TR1 |

TCON.6 |

Біт керування таймера 1. Установлюється /

скидається програмою для пуску/зупинки |

|

TF0 |

TCON.5 |

Прапор переповнення таймера 0. Встановлюється

апаратно. Скидається при обслуговуванні переривання |

|

TR0 |

TCON.4 |

Біт керування таймера 0. Установлюється / скидається

програмою для пуску/зупинки таймера/лічильника |

|

IE1 |

TCON.3 |

Прапор фронту переривання 1. Встановлюється

апаратно, коли детектується зріз зовнішнього

сигналу INT1. Скидається при обслуговуванні переривання |

|

IT1 |

TCON.2 |

Біт керування типом переривання 1. Установлюється /

скидається програмно для специфікації запиту INT1 (зріз/низький рівень) |

|

IE0 |

TCON.1 |

Прапор фронту переривання 0. Установлюється по

зрізі сигналу INT0. Скидається при обслуговуванні переривання |

|

IT1 |

TCON .0 |

Біт керування типом переривання 0. Установлюється /

скидається програмно для специфікації запиту INT0 (зріз/низький рівень) |

Як випливає з

опису керуючих біт TMOD, для обох Т/С режими роботи 0, 1 і 2 однакові. Режими 3 для Т/С і Т/С1 різні. Розглянемо роботу

Т/С в кожному з режимів.

Режим 0. Перевід будь-якого Т/С в режим 0

робить його схожим на восьми бітний лічильник, до входу якого підключений

п'ятий-бітний переддільник частоти на 32. У цьому

режимі таймерний регістр має розрядність 13 біт. При переході зі стану

"всі одиниці" у стан "усі нулі" установлюється прапор переривання

від таймера TF1. Вхідний синхросигнал таймера 1

дозволений (надходить на вхід Т/С1), коли керуючий біт TR1 встановлений у 1 або

керуючий біт GATE (блокування) дорівнює 0, або на зовнішній вивід запиту переривання

INT1 надходить рівень 1.

Режим 1. Робота будь-якого Т/С в цьому режимі

така ж, як і в режимі 0, за винятком того, що таймерний регістр має розрядність

16 біт.

Режим 2. У цьому режимі робота організована таким чином, що

переповнення (перехід зі стану "всі одиниці" у стан, "усі

нулі") восьмибітного лічильника TL1 приводить не

тільки до установки прапора TF1, але й автоматично перезавантажує в TL1 уміст

старшого байта (TH1) таймерного регістра, що попередньо було задано програмним

шляхом. Перевантаження залишає вміст TH1 незмінним. У режимі 2 Т/С0 і Т/С1

також працюють зовсім однаково.

Режим 3. У режимі 3 Т/С0 і Т/С1 працюють по-різному. Т/С1

зберігає незмінним свій поточний вміст. У режимі 3 TL0 і TH0 функціонують як

два незалежних восьмибітних лічильники. Роботу TL0

визначають керуючі біти Т/С0 (С/Т, GATE TR0), вхідний сигнал INT0 і прапор

переповнення TF0. Роботу TH0, що може виконувати тільки функції таймера

(підрахунок машинних циклів), визначає керуючий біт TR1. При цьому TH0

використовує прапор переповнення TF1. Режим 3 використовується в тих випадках,

коли потрібно наявність додаткового восьми бітного таймера або лічильника

подій. Можна вважати, що в цьому режимі мікроконтролер

8051 має у своєму складі три таймери/лічильника. У випадку ж, якщо Т/С0

використовується в режимі 3, Т/С1 може бути виключений або переведений у режим

0, 1, 2 або може бути використаний послідовним портом як генератор частоти

передачі.

У модернізованих

моделях мікроконтролерів сімейства MCS-51 може матися

третій таймер лічильник T/C2 і/або блок програмних лічильників PCA, що теж

можуть бути використані для відліку часових інтервалів.

5 Послідовний порт мікроконтролера

Через універсальний асинхронний прийомопередавач UART (Universal Asynchronous Receiver-Transmitter) здійснюються прийом і

передача інформації, що представлена послідовним кодом (молодшими бітами

вперед), у повному дуплексному режимі обміну. До складу прийомопередавача,

що часто називають послідовним портом входять приймаючий і передавальний

регістри зсуву, а також спеціальний буферний регістр (SBUF) прийомопередавача.

Крім того, роботою послідовного

порту керують два службових регістри –

регістр керування/статусу прийомопередавача SCON та біт SMOD регістра керування

потужністю PCON

Запис байта в буфер приводить до

автоматичного запису байта в регістр зсуву передавача і ініціює початок

передачі байта. Наявність буферного регістра приймача дозволяє об’єднати

операцію читання раніше прийнятого байта з прийомом чергового. Але якщо до

моменту закінчення прийому байта попередній не був зчитаний з SBUF, то він буде

загублений.

Послідовний порт 8051 може

працювати в чотирьох різних режимах.

- Режим 0. Інформація і

передається, і приймається через вивід входу приймача (RXi

TXi).

Приймаються та передається 8 біт даних. Через вивід виходу

передавача TXD видаються імпульси зсуву,

що супроводжують кожен біт. Частота передачі біта інформації дорівнює 1/12

частоти кварцового резонатора.

- Режим 1. У цьому режимі

передаються через вивід TXD або приймаються через RXD 10 біт інформації:

старт-біт (0), 8 біт даних і стоп-біт (1) при прийомі інформації в біт RB8

регістра керування/статусу прийомопередавача

SCON заносяться стоп-біт. Швидкість прийому/передачі – величина змінна і

задається таймером.

- Режим 2. У цьому режимі через

вивід TXD передаються або через RXD приймаються 11 біт інформації:

старт-біт, 8 біт даних, програмований дев'ятий біт і стоп-біт. При

передачі дев'ятий біт даних може приймати значення або 0, або 1, наприклад, для підвищення ймовірності

передачі шляхом контролю парності в ньому може бути поміщене значення

ознаки паритету зі слова стану програми (PSW.0). При прийомі дев'ятий біт

даних розміщується в біті RB8 SCON, а стоп-біт, на відміну від режиму 1,

губиться. Частота прийому/передачі вибирається програмою і може бути рівна

або 1/32, або 1/64 частоти резонатора в залежності від керуючого біта

SMOD.

- Режим 3. збігається з режимом 2 у

всіх деталях, за винятком частоти прийому/передачі, що є величиною

перемінної і задається таймером.

В усіх випадках передача ініціалізується інструкцією, у якій дані переміщаються в

SBUF. Прийом ініціалізується при виявленні перепаду з

1 у 0 на вході приймача. При цьому в режимі 0 цей перехід повинний

супроводжуватися виконанням умов R1 = 0 і REN= 1, а для інших режимів - REN =

1.

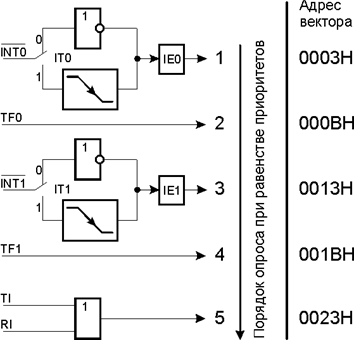

6 Система переривань мікроконтролера 8051

Спрощена схема переривань 8051 наведена

на рисунку 3. Зовнішні переривання INT0 і INT1 можуть бути викликані або

рівнем, або переходом сигналу з 1 у 0 на входах 8051 у залежності від значень

керуючих біт IT0 і IT1 у регістрі TCON. Від зовнішніх переривань установлюються

прапори IE0 і IE1 у регістрі TCON, що ініціюють виклик відповідної програми

обслуговування переривання. Скидання цих прапорів виконується апаратно тільки в

тому випадку, якщо переривання було викликано по переходу (зрізу) сигналу. Якщо

ж переривання викликане рівнем вхідного сигналу, то скиданням прапора І повинна

керувати відповідна підпрограма обслуговування переривання шляхом впливу на

джерело переривання з метою зняття їм запиту.

Прапори запитів переривання від

таймерів TF0 і TF1 скидаються автоматично при передачі керування підпрограмі

обслуговування. Прапори запитів переривання RI і TI встановлюються блоком

керування прийомопередавача апаратно, але скидатися

повинні програмним шляхом.

Переривання можуть бути викликані або

скасовані програмою, тому що всі названі прапори програмно доступні і можуть

бути встановлені/ скинуті програмою з тим же результатом, як якби вони були

встановлені/скинуті апаратними засобами.

У блоці регістрів спеціальних

функцій є два регістри, призначених для керування режимом переривань IE і

рівнями пріоритету IP. Можливість програмної установки/скидання будь-якого

керуючого біта в цих двох регістрах робить систему переривань 8051 винятково

гнучкої.

У більш складних модифікаціях мікроконтролерів сімейства MCS-51 кількість периферійних

пристроїв збільшено, що приводить до необхідності використовувати один вектор

переривання для декількох пристроїв (поділ підпрограм обслуговування переривань

у цьому випадку необхідно реалізувати програмно), або додати ще два регістри -

режиму (маски) і пріоритету переривань.

Рисунок 3 – Схема організації переривань мікроконтролера 8051

Таблиця 7 –Регістр масок переривання (IE).

|

Символ |

Позиція |

Ім'я і призначення |

|

EA |

IE.7 |

Зняття блокування переривання. Скидається,

програмно для заборони всіх переривань незалежно від станів IE.4 - IE.0 |

|

|

IE.6 |

Не

використовується |

|

|

lE.5 |

Не

використовується |

|

ES |

IE.4 |

Біт дозволу переривання,

від прийомопередавача Встановлення/скидання

програмою для дозволу/заборони переривань від прапорів TI чи RI . |

|

ET1 |

IE.3 |

Біт дозволу переривання від таймера.

Встановлення /скидання програмою для дозволу/заборони переривань від таймера

1 |

|

EX1 |

IE.2 |

Біт дозволу зовнішнього переривання 1.

Встановлення /скидання програмою для дозволу/заборони переривання 1 |

|

ET0 |

IE.1 |

Біт дозволу переривання від таймера 0.

Встановлення /скидання програмою для дозволу/заборони переривань від таймера

0 . |

|

EX0 |

IE.0 |

Біт дозволу зовнішнього переривання 0.

Встановлення /скидання програмою для дозволу/заборони переривання 0 |

Таблиця 8 – Регістр пріоритетів

переривань (IP)

|

Символ |

Позиція |

Ім'я і призначення |

|

- |

IP.7 - IP.5 |

Не використовується |

|

PS |

IP.4 |

Біт пріоритету прийомопередавача. Встановлення/скидання програмою для

присвоювання перериванню від прийомопередавача

вищого/нижчого пріоритету |

|

РТ1 |

IP.3 |

Біт пріоритету

таймера 1. Встановлення /скидання програмою для присвоювання перериванню від

таймера 1 вищого/нижчого пріоритету |

|

РХ1 |

IP.2 |

Біт пріоритету

зовнішнього переривання 1. Встановлення /скидання програмою для присвоювання

вищого/нижчого пріоритету зовнішньому перериванню INT1 |

|

РТ0 |

IP.1 |

Біт пріоритету

таймера 0. Встановлення /скидання програмою для присвоювання перериванню від

таймера 0 вищого/нижчого пріоритету |

|

РХ0 |

IP.0 |

Біт пріоритету

зовнішнього переривання 0. Встановлення /скидання програмою для присвоювання

вищого/нижчого пріоритету зовнішньому перериванню INT0 |

Система переривань формує апаратний

виклик (LCALL) відповідної підпрограми обслуговування, якщо вона не заблокована

однією з наступних умов:

- у даний момент обслуговується запит переривання рівного або вищого

рівня пріоритету;

- поточний машинний цикл — не останній у циклі команди, що виконується;

- виконується команда RETI або будь-яка команда, зв'язана зі

звертанням до регістрів IЕ чи IP.

Відзначимо, що якщо прапор

переривання був установлений, але по одному з зазначених вище умов не одержав

обслуговування і до моменту закінчення блокування вже скинутий, то запит

переривання губиться і ніде не запам'ятовується.

За апаратно сформованим кодом LCALL

система переривання поміщає в стек тільки вміст лічильника команд (PC) і

завантажує в нього адресу вектора відповідної підпрограми обслуговування. За

адресою вектора повинна бути розташована команда безумовної передачі керування

(JMP) до початкової адреси підпрограми обслуговування переривання. У разі

потреби вона повинна починатися командами запису в стек (PUSH) слова стану

програми (PSW), акумулятора, покажчика

даних і т.д. і повинна закінчуватися командами відновлення зі стека (POP).

Підпрограми обслуговування переривання повинні завершуватися командою RETI, по

якій у лічильник команд перезавантажується зі стека збережена адреса повернення

в основну програму. Команда RET також повертає керування перерваній основній

програмі, але при цьому не знімуть блокування переривань, що приводить до

необхідності мати програмний механізм аналізу закінчення процедури

обслуговування даного переривання.