Компаратор. ЦАП. АЦП

2 Цифроаналогові перетворювачі

2.2 Інтерфейси цифроаналогових

перетворювачів

3 Аналого-цифрові перетворювачі

3.5 Вбудований АЦП мікроконтролерів

AVR

1 Компаратор

Модуль

аналогового компаратора входить практично в усе сучасні МК. Фізично компаратор

є швидкодіючим операційним підсилювачем з великим коефіцієнтом підсилення,

частотною корекцією і виходом на цифровий логічний елемент. Зворотний зв'язок

через зовнішній резистор з виходу на вхід не передбачається. Вихідний сигнал

компаратора має НИЗЬКИЙ/ВИСОКИЙ логічний рівень, який запам'ятовується в

програмно-доступному регістрі.

Компаратор

порівнює між собою по амплітуді дві напруги, що присутні на його позитивному і

негативному входах. Результат порівняння читається з внутрішнього регістра МК і

може служити джерелом переривання.

В

цілому мікроконтролерний компаратор дуже схожий на

звичайний компаратор на ІМС, але тільки вихідний сигнал OUT, як правило,

захований усередині. Ще одна відмінність - лінії аналогового компаратора

являються сумісними і можуть настроюватися як цифрові виходи.

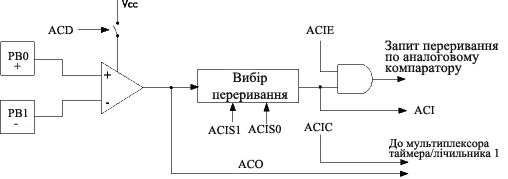

Рисунок 1.1 – Структурна схема аналогового компаратора МК ATtiny2313

Аналоговий компаратор МК ATtiny2313 має два

входи – AІN0 і AІN1, на які надходять аналогові

сигнали, що порівнюються за величиною напруги. До складу аналогового

компаратора крім базового компаратора входить регістр керування стану ACSR

($08) і елементи, що керують роботою схеми. Результатом роботи компаратора є

запит переривання ANA COMP, що формується, коли різниця значень напруг на

входах компаратора змінює знак. Структурна схема аналогового компаратора

зображена на рис. 1.

Базовий компаратор

має два входи - позитивний (+) і негативний (-). Вихідний сигнал

базового компаратора АСО має одиничне значення, якщо напруга на вході

"+" більше напруги на вході "-" (якщо PB0>PB1, то ACO=1).

Схема керування

при визначеній зміні сигналу АСО встановлює в одиничний стан розряд ACІ регістра ACSR і

при одиничному стані розряду ACІ регістра ACSR у блок перериванні надходить

запит переривання ANA COMP. Розряд ACІ скидається в нульовий стан апаратно при

переході до виконання програми, що

перериває, чи програмно шляхом запису одиниці в розряд ACІ.

Вибір виду зміни сигналу АСО на вході схеми керування,

при якому формується запит переривання, визначається комбінацією стану розрядів

ACІS0 і ACІS1 регістра ACSR

При установці в одиничний стан розряду ACD регістра

ACSR відключається живлення базового компаратора і зменшується струм споживання

мікроконтролера.

Таблиця 1.1

– Регістр статусу і керування аналогового компаратора ACSR (The Analog Comparator Control and Status Register)

|

Біти |

|

|

||||||||

|

$08 ($28) |

|

ACSR |

||||||||

|

Читання/Запис |

|

|

||||||||

|

Початковий стан |

|

|

- Bit 7 - ACD: Analog Comparator Disable – Заборона аналогового компаратора (якщо ACD=1, то компаратор відключений)

- Bit 5 - ACO: Analog Comparator Output - Вихід аналогового компаратора.

- Bit 4 - ACI: Analog Comparator Interrupt Flag - Прапор переривання по аналоговому

компаратору. Даний

біт встановлюється в стан 1 у випадку формування компаратором переривання,

обумовленого ACІ1 і ACІ0.

- Bit 3 - ACIE: Analog Comparator Interrupt Enable - Дозвіл переривання по аналоговому

компаратору.

- Bit 2 - ACIC: Analog Comparator Input Capture enable - Дозвіл входу захоплення аналогового

компаратора.

- Bits 1, 0 - ACIS1, ACIS0: Analog Comparator Interrupt Mode Select - Вибір режиму переривання по аналоговому

компаратору.

Таблиця 1.2

– Установки біт ACIS1/ACIS0.

|

ACIS1 |

ACIS0 |

Режим

переривання |

|

0 |

0 |

Переривання по перемиканню виходу

компаратора |

|

0 |

1 |

Зарезервовано |

|

1 |

0 |

Переривання по спадаючому фронту на

виході компаратора |

|

1 |

1 |

Переривання по наростаючому фронту на

виході компаратора |

;Initial Analog Comparator Setup

(assumes ACIE = 0)

sbi ACSR,ACI ; write a " 1" to the ACI flag to clear it

sei ; enable global interrupts

sbi ACSR,ACIS0 ; enable interrupt on

sbi ACSR,ACIS1 ; rising output edge

sbi ACSR,ACIE ; enable Analog Comparator interrupt

Застосування

аналогового компаратора виправдане в таких випадках:

- при

малій амплітуді вхідних сигналів 30...300 мВ;

- при

необхідності порівняння рівнів двох сигналів ("більше/менше");

- при

підвищених вимогах до швидкодії, коли внутрішній АЦП вже не справляється зі

своїми обов'язками.

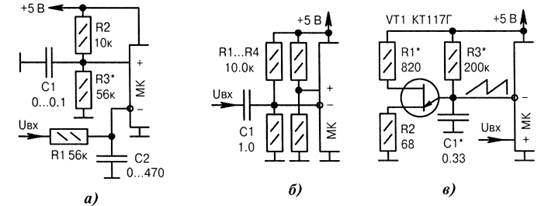

На

рисунку 1.2, а...н показані схеми подання сигналів

на компаратор МК.

а)

дільником R2, R3 встановлюється поріг

спрацьовування компаратора. Необхідність застосування конденсаторів С1, С2, що

фільтрують, визначається експериментально по відсутності неправдивих

перемикань;

б)

прийом змінної напруги малої амплітуди 50... 100 мВ. Якщо форма вхідного сигналу

"синусоїда", то відбувається її програмне перетворення в

"прямокутник";

в)

пилкоподібна напруга формується одноперехідним

транзистором VT1. Усередині МК програмно підраховується час досягнення рівності

напруги на обох входах;

г) двохланковий

ФНЧ на елементах R3, С1, R5, С2 обмежує спектр вхідного сигналу. Змінним

резистором R4 встановлюється поріг спрацьовування компаратора;

д) компаратор приймає вхідний сигнал

через оптопару VU1. У паузах роботи МК виставляє на

виході НИЗЬКИЙ рівень, щоб понизити струм споживання через резистори R1...R3;

е) в початковому стані на виході МК

ВИСОКИЙ рівень. Як тільки аналоговий компаратор "спрацює", на виході

МК виставляється НИЗЬКИЙ рівень, щоб відсікти флуктуації сигналу. Утворюється

гістерезис напруги UГ[В] = 5R2R3/(R2R3+R3R4+R2R4), де R2...R4 виражені в кілоомах, а число

"5" відповідає напрузі живлення МК у вольтах;

Рисунок 1.2 –Схеми подачі сигналів на аналоговий

компаратор мікроконтролера

ж) пилкоподібну

напругу формує сам МК через ключ VT2 (скидання) і генератор стабильного

струму на елементах VT1, R1, R2, HL1. Світлодіод

також служить індикатором живлення;

з)

аналогічно, але з генератором стабільного струму на мікросхемі DA1.

Пилкоподібна напруга може формуватися з певним періодом (режим автоматичного

виміру) або одноразово (режим поодинокого виміру). У останньому випадку для

економії енергії в паузах на негативному виводі компаратора має бути ВИСОКИЙ

рівень;

и)

"дельта-модулятор" на основі компаратора МК. Вхідний аналоговий

сигнал програмно перетворюється у вихідний цифровий сигнал Ubux,

що модулюється методом ШІМ;

к)

вхідний сигнал може одночасно поступати на компаратор і на звичайну лінію порта МК, наприклад, для повторної перевірки показів або

для організації сервісних функцій;

л)

поріг спрацьовування аналогового компаратора МК залежить від температури

довкілля (терморезистор R1). Резистор R2 лінеаризує температурну характеристику;

м)

пилкоподібна (експоненціальна) напруга на конденсаторі С1 формується за

допомогою подання ВИСОКОГО/НИЗЬКОГО рівня на верхньому за схемою виводі

резистора R1;

н)

аналогічно, але з використанням поєднаної лінії порту, через яку періодично

розряджається конденсатор С1 НИЗЬКИМ рівнем.

2 Цифроаналогові перетворювачі

2.1 Загальні

відомості

Цифроаналоговий

перетворювач (ЦАП) призначений для перетворення числа, визначеного, як правило,

у вигляді двійкових кодів, у

напругу або струм пропорційно значенню цифрового коду.

Дуже часто ЦАП входить до складу

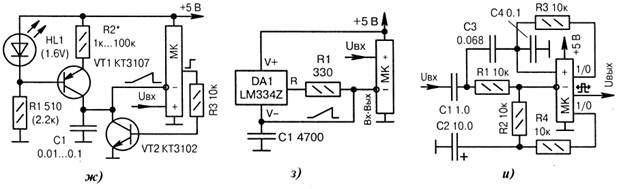

МПС. У цьому випадку, якщо не потрібна висока швидкодія, цифроаналогове

перетворення може бути дуже просто здійснено за допомогою ШІМ. Схема ЦАП з ШІМ

наведена на рисунку

2.1.

Рисунок 2.1–

ЦАП з широтно-імпульсною модуляцією:

Рисунок 2.1–

ЦАП з широтно-імпульсною модуляцією:

а) структурна схема; б) часова діаграма

Найпростіше організовується цифроаналогове перетворення в тому випадку, якщо МК має

вбудовану функцію широко-імпульсного перетворення (наприклад, AT90S8515 фірми Atmel або 87C51GB фірми Intel). Вихід ШІМ керує ключем S. У залежності від заданої розрядності перетворення (для МК

AT90S8515 можливі режими 8, 9 і 10 розрядів) контролер за допомогою власного

таймера/лічильника формує послідовність імпульсів, відносна тривалість яких ![]() визначається співвідношенням (формула 1.1):

визначається співвідношенням (формула 1.1):

![]() , (1.1)

, (1.1)

де N – розрядність перетворення, а D – код перетворення.

Фільтр нижніх частот згладжує

імпульси, виділяє середнє значення напруги. У результаті вихідна напруга

перетворювача (формула 1.2):

(1.2)

(1.2)

Розглянута схема забезпечує ідеальну лінійність перетворення, не містить

прецизійних елементів (за винятком джерела опорної напруги). Основний її

недолік – низька швидкодія.

Паралельні

ЦАП мають більшу швидкодію і тому вони можуть застосовуватися для більш

широкого кола задач. Більшість схем паралельних ЦАП реалізовано на додаванні струмів, що

пропорційні вазі цифрових двійкових розрядів, причому повинні додаватись тільки

струми тих розрядів, значення яких дорівнює 1.

2.2 Інтерфейси цифроаналогових перетворювачів

Важливу

частину ЦАП складає цифровий інтерфейс, тобто схеми, що забезпечують зв'язок

входів керування ключів з джерелами цифрових сигналів. Структура цифрового

інтерфейсу визначає спосіб підключення ЦАП до джерела вхідного коду, наприклад,

МП чи МК. Властивості цифрового інтерфейсу безпосередньо впливають і на форму

вихідної характеристики ЦАП. Так, неодночасність надходження розрядів вхідного

слова на входи керування ключів перетворювача приводить до появи вузьких

викидів ("голок") у

вихідному сигналі при зміні коду.

При

керуванні ЦАП від цифрових пристроїв з жорсткою логікою входів керування

ключів, ЦАП можуть бути безпосередньо підключені до виходів цифрових пристроїв,

тому в багатьох ІС ЦАП, особливо ранніх (572ПА1, 594ПА1, 1108ПА1, AD565),

будь-яка істотна цифрова частина відсутня. Якщо ж ЦАП входить до складу МПС і

отримує вхідний код від шини даних, то він повинен бути забезпечений схемами,

що дозволяють приймати вхідне слово від шини даних, зберігати його до отримання

іншого слова, комутувати відповідно до цього слова ключі ЦАП. Для керування

процесом завантаження вхідного слова ЦАП повинен мати відповідні входи

керування і схему керування. Залежно від способу завантаження вхідного слова в

ЦАП розрізняють перетворювачі з послідовним і паралельним інтерфейсами вхідних

даних.

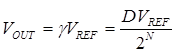

ЦАП з послідовним інтерфейсом

вхідних даних, крім власне ЦАП, містить на кристалі послідовний регістр

завантаження, паралельний регістр зберігання та логіку керування (рис. 2.2, а). При активному рівні сигналу ![]() (в даному випадку низькому) вхідне слово

довжиною N (рівною розрядності ЦАП)

завантажується по лінії DI в регістр

зсуву під керуванням тактової послідовності CLK.

Після закінчення завантаження, виставивши активний рівень на лінію

(в даному випадку низькому) вхідне слово

довжиною N (рівною розрядності ЦАП)

завантажується по лінії DI в регістр

зсуву під керуванням тактової послідовності CLK.

Після закінчення завантаження, виставивши активний рівень на лінію ![]() ,

вхідне слово записують в регістр зберігання, виходи якого безпосередньо керують

ключами ЦАП. Для того, щоб мати можливість передавати по одній лінії вхідні

коди на декілька ЦАП, останній розряд регістра зсуву з'єднується з виводом ІС.

Цей вивід підключається до входу DI наступного ЦАП і так далі. Коди вхідних

слів передаються, починаючи з коду найостаннішого перетворювача.

,

вхідне слово записують в регістр зберігання, виходи якого безпосередньо керують

ключами ЦАП. Для того, щоб мати можливість передавати по одній лінії вхідні

коди на декілька ЦАП, останній розряд регістра зсуву з'єднується з виводом ІС.

Цей вивід підключається до входу DI наступного ЦАП і так далі. Коди вхідних

слів передаються, починаючи з коду найостаннішого перетворювача.

Як приклад, на рисунку 2.2, б наведена часова діаграма, що відображає процес

завантаження вхідного слова в ЦАП AD7233. Мінімально допустимі значення

інтервалів часу (порядку 50 нс), позначених на епюрах, вказуються в технічній

документації на ІС.

Рисунок 2.2 – ЦАП з послідовним інтерфейсом:

а) функціональна схема; б) часова

діаграма

Після закінчення завантаження МК

змінює рівень на вході ![]() , як

це показано на рисунку 2.2, б.

Виставивши активний рівень на вході

, як

це показано на рисунку 2.2, б.

Виставивши активний рівень на вході ![]() ,

ЦАП забезпечує пересилання вхідного

коду з регістра зсуву ЦАП в регістр зберігання. Час завантаження

залежить від тактової частоти МК і зазвичай складає одиниці мікросекунд. У

випадку, якщо коливання вихідного сигналу ЦАП під час завантаження допустимі,

вхід

,

ЦАП забезпечує пересилання вхідного

коду з регістра зсуву ЦАП в регістр зберігання. Час завантаження

залежить від тактової частоти МК і зазвичай складає одиниці мікросекунд. У

випадку, якщо коливання вихідного сигналу ЦАП під час завантаження допустимі,

вхід ![]() можна з'єднати з загальною точкою схеми.

можна з'єднати з загальною точкою схеми.

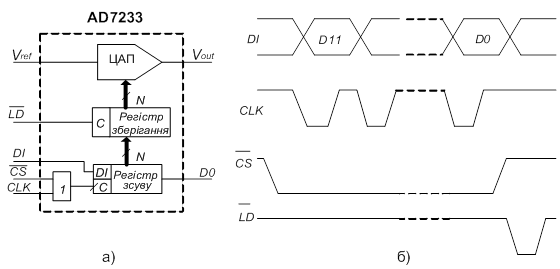

На рисунку 2.3 наведений варіант схеми підключення перетворювача з

послідовним інтерфейсом до МК. На час завантаження вхідного слова в ЦАП через

послідовний порт МК, до якого можуть бути також підключені і інші приймачі, на

вхід ![]() (вибір кристала) подається активний рівень з

однієї з ліній введення/виведення МК.

(вибір кристала) подається активний рівень з

однієї з ліній введення/виведення МК.

Рисунок 2.3 – Підключення ЦАП з послідовним

інтерфейсом до МК MCS51

Стосовно ЦАП з паралельним інтерфейсом вхідних даних

можна сказати, що частіше використовуються два варіанти. У першому варіанті на N входів даних N-розрядного ЦАП подається вхідне слово повністю. Інтерфейс такого

ЦАП містить два регістри зберігання і схему керування (рис. 2.4, а) Два регістри зберігання потрібні,

якщо пересилання вхідного коду до ЦАП і установлення вихідного аналогового

сигналу, відповідного цьому коду, повинні бути розділені в часі.

Подача на вхід асинхронного скидання ![]() сигналу низького рівня приводить до скидання

першого регістра і, відповідно, вихідної напруги ЦАП.

сигналу низького рівня приводить до скидання

першого регістра і, відповідно, вихідної напруги ЦАП.

Рисунок 2.4 – ЦАП з паралельним інтерфейсом:

а) структурна схема; б) часова

діаграма

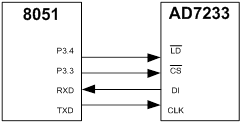

Приклад блок-схеми підключення 12-розрядного ЦАП

МАХ507 до 16-розрядного МП наведений на рисунку 2.5. Процесор посилає вхідний

код в ЦАП як в елемент пам'яті даних. Спочатку з шини адреси/даних AD надходить

адреса ЦАП, яка фіксується регістром за командою з виходу ALE МП і, після дешифрування,

активізує вхід ![]() ЦАП. Зразу після цього МП подає на шину AD вхідний код ЦАП і потім сигнал запису

на вхід

ЦАП. Зразу після цього МП подає на шину AD вхідний код ЦАП і потім сигнал запису

на вхід ![]() .

.

Рисунок 2.5 – Підключення ЦАП з

паралельним інтерфейсом до МП Intel 8086

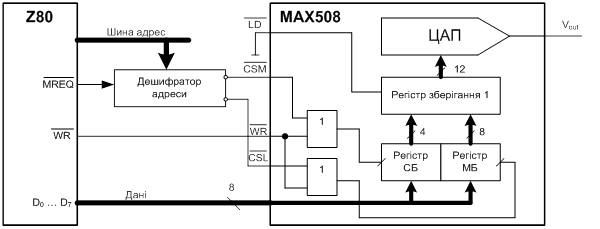

Для підключення багаторозрядних

ЦАП до восьмирозрядних МП і МК використовується

другий варіант паралельного інтерфейсу. Він передбачає наявність двох

паралельних завантажувальних регістрів для прийому молодшого байта (МБ)

вхідного слова і старшого байта (СБ)

(рис. 2.6). Пересилання байтів вхідного слова до завантажувальних регістрів

може відбуватися у будь-якій

послідовності.

Рисунок 2.6 – Підключення ЦАП з паралельним

інтерфейсом другого типу до восьмирозрядного МП

3 Аналого-цифрові

перетворювачі

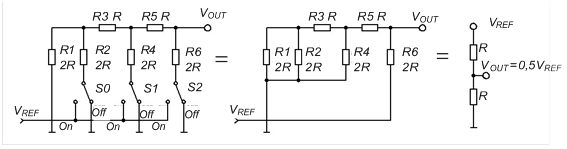

На рисунку

3.1 показаний простий резистивний АЦП східчастого типу з трьома ключами.

Резистори складені в R/2R конфігурації. Номінали резисторів не важливі; опір може бути

10 кОм, 100 кОм і тому подібне. Кожен з ключів S0...S2

може підключати один вивід одного резистора номіналом 2R між землею і вхідною опорною напругою, VREF. На рисунку 3.1 показано, що відбувається, коли S2 замкнутий "ON" (з’єднаний із VREF), а S0 і S1 розімкнені

"OFF" (з’єднані із землею). У результаті падіння напруги на

послідовно-паралельній резистивній ділянці остаточна вихідна напруга (V0) стає рівною 0,5VREF. Можна так само

обчислити V0 для всіх інших

комбінацій ключів (табл. 3.1).

Якщо положення (замкнутий-розімкнутий) трьох ключів уявити, як цифрове

слово з трьох бітів, тоді можемо переписати таблицю, використовуючи позначення

ON = 1 (замкнутий), OFF = 0 (розімкнутий) (табл. 3.2).

Рисунок 3.1 – Бітові АЦП

Таблиця 3.1 – Залежність

вихідної напруги відносно стану ключів

|

Положення |

Вихідна напруга VOUT |

||

|

S2 |

S1 |

S0 |

|

|

OFF |

OFF |

OFF |

0 |

|

OFF |

OFF |

ON |

0,125·VREF(l/8-VREF) |

|

OFF |

ON |

OFF |

0,25·VREF(2/8-VREF) |

|

OFF |

ON |

ON |

0,375·VREF(3/8-VREF) |

|

ON |

OFF |

OFF |

0,5·VREF(4/8-VREF) |

|

ON |

OFF |

ON |

0,625·VREF(5/8-VREF) |

|

ON |

ON |

OFF |

0,75·VREF(6/8-VREF) |

|

ON |

ON |

ON |

0,875·VREF(7/8-VREF) |

Таблиця 3.2 – Змінена таблиця

залежності вихідної напруги відносно стану ключів

|

Положення ключа |

Логічний еквівалент |

S0...S2 чисельний еквівалент |

||||

|

S2 |

S1 |

S0 |

S2 |

S1 |

S0 |

|

|

OFF |

OFF |

OFF |

0 |

0 |

0 |

0 |

|

OFF |

OFF |

ON |

0 |

0 |

1 |

1 |

|

OFF |

ON |

OFF |

0 |

1 |

0 |

2 |

|

OFF |

ON |

ON |

0 |

1 |

1 |

3 |

|

ON |

OFF |

OFF |

1 |

0 |

0 |

4 |

|

ON |

OFF |

ON |

1 |

0 |

1 |

5 |

|

ON |

ON |

OFF |

1 |

1 |

0 |

6 |

|

ON |

ON |

ON |

1 |

1 |

1 |

7 |

Таким чином, вихідна напруга є

поданням комбінації положень ключів. Кожен додатковий біт у таблиці додає VREF/8

до загальної напруги. Або, іншими словами, вихідна напруга дорівнює двійковому

числу комбінації S0...S2, помноженому на VREF/8. Такий 3-бітовий АЦП

має 8 можливих станів, і кожен крок напруги складає VREF/8.

Якщо додати ще одну R/2R пару і ще один ключ до схеми,

отримаємо схему з чотирма ключами і шістнадцятьма кроками по VREF/16

вольт кожна. Схема з вісьмома ключами має 256 рівнів кожний по VREF/256

вольт. Замінивши механічні ключі в схемі на електронні, можна створити

повноцінний інтегральний АЦП.

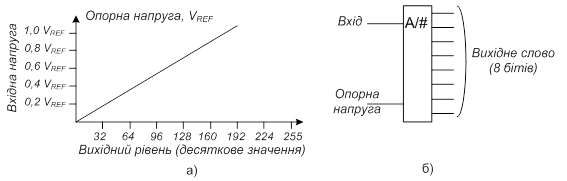

Для передачі аналогового сигналу до МПС

використовують АЦП. АЦП сприймає аналоговий сигнал, напругу або струм і

перетворює його в цифрове слово, зрозуміле МП (рис. 3.2, а). На рисунку 3.2, б наводиться умовне зображення АЦП,

який має вхід опорної напруги VREF (reference)

та вхід, куди подається сигнал. АЦП має

один вихід – цифрове слово розмірністю 8 бітів, що являє в цифровій формі

вхідну величину.

Рисунок 3.2 –

До розгляду роботи АЦП

Опорна напруга, VREF – максимальна величина напруги, яку АЦП може

перетворити. АЦП, що зображений на рисунку 1.62, може перетворити напругу з

величинами від 0 до VREF. Цей діапазон напруги поділений на 256

рівнів або кроків. Розмір одного кроку задається так:

![]() (1.3)

(1.3)

8-бітовий АЦП подає аналоговий сигнал цифровим

словом. Старший значущий біт цього слова (біт 7) показує, чи вища вхідна

напруга, ніж VREF/2 (2,5 В

при VREF = 5 В). Кожен

наступний біт (від біта 6 до біта 0, який буде молодшим значущим бітом – least significant bit, LSB) є половиною значення попереднього, як показано в

таблиці 3.3.

Таблиця 3.3 – Подання аналогового входу цифровим словом

|

Біт |

Біт 7 |

Біт 6 |

Біт 5 |

Біт 4 |

Біт 3 |

Біт 2 |

Біт 1 |

Біт 0 |

|

Напруга [В] |

2,5 |

1,25 |

0,625 |

0,3125 |

0,156 |

0,078 |

0,039 |

0,0195 |

Так, маючи цифрове слово 0010 1100,

можна визначити величину напруги (таблиця 3.4).

Таблиця 3.4 – Відповідність цифрового слова певним значенням

|

Біт |

Біт 7 |

Біт 6 |

Біт 5 |

Біт 4 |

Біт 3 |

Біт 2 |

Біт 1 |

Біт 0 |

|

Напруга[В] |

2,5 |

1,25 |

0,625 |

0,3125 |

0,156 |

0,078 |

0,039 |

0,0195 |

|

Вихідна величина |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

Додавши напругу, що відповідає кожному одиничному біту, отримуємо реальну напругу (формула 1.4).

![]() (1.4)

(1.4)

Роздільна здатність АЦП

визначається опорною напругою і розрядністю слова. Роздільна здатність –

це найменша напруга, яка може бути виміряна АЦП і

визначає точність перетворення. Роздільна здатність – це найменший крок, може бути визначена діленням VREF на число можливих

величин перетворення.

Наприклад, для 8-бітного АЦП з VREF = 5 В роздільна

здатність дорівнює 0,0195 В (19,5 мВ). Це означає, що будь-яка вхідна напруга,

менша 19,5 мВ, дасть на виході 0. Вхідна напруга між 19,5 і

39 мВ приведе до 1 на виході. Між 39 і 58,6 мВ – до 2 і так далі. Роздільна

здатність може бути покращена зменшенням VREF.

Зміна VREF з 5 до 2,5 В дасть роздільну здатність 2,5/256 або 9,7

мВ. Проте максимальна напруга

вимірювання тепер складе не 5, а 2,5 В.

Є лише один шлях збільшення роздільної здатності без зміни опорної напруги

– використання АЦП з більшою розрядністю слова. Так 10-бітовий АЦП з опорною

напругою 5 В має 210, або 1024 можливих вихідних двійкових кодів.

Роздільна здатність складе 5 В/1024 або 4,88 мВ.

Існує декілька типів АЦП, що

працюють з різними швидкостями, мають

різні інтерфейси і забезпечують різну

точність. Розглянемо їх особливості.

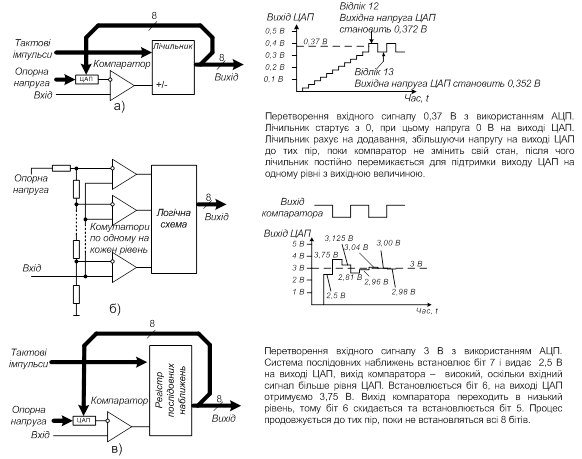

Слідкувальний АЦП складається з

компаратора, реверсивного лічильника, керованого компаратором, і ЦАП.

Компаратор порівнює вхідну напругу з вихідною напругою ЦАП і керує напрямком

лічби реверсивного лічильника (+/-). Якщо вхідна напруга більша, ніж напруга

ЦАП, лічильник під дією тактових імпульсів, що надходять на його вхід (рис.

1.63, а) рахує на додавання (+),

якщо ж менше напруги ЦАП, лічильник рахує на віднімання (-).

Вхід ЦАП з’єднаний з виходом

лічильника. Припустимо VREF = 5 В.

Це означає, що перетворювач зможе працювати в діапазоні вхідної напруги 0...5

В. Якщо старший значущий біт вхідного слова ЦАП дорівнює 1, то VЦАП = 2,5 В. Якщо наступний

біт дорівнює 1, додається 1,25 В, в результаті

встановлюється 3,75 В. Кожен наступний біт додає половину вихідної напруги, що

відповідає попередньому біту. Таким чином, вхідні біти ЦАП відповідають певній

напрузі (табл. 3.3, 3.4).

На рисунку 3.3, а показано, як слідкувальний

АЦП обробляє постійний сигнал з рівнем VBX

= 0,37 В. Лічильник стартує з нуля, при цьому вихід компаратора знаходиться у

високому логічному рівні. Лічильник рахує на додавання з кожним тактовим

імпульсом, ступінчасто піднімаючи VЦАП. Коли лічильник проходить

двійкову величину, яка є VBX,

то компаратор перемикається, і лічильник починає рахувати на віднімання. У

результаті, лічильник хитається в овколі величини,

яка є VBX.

Головний недолік слідкувальних АЦП – низька швидкість перетворення.

Перетворення може зайняти до 256 тактів 8-бітового виходу, 1024 такти для

10-бітового значення і так далі. До того ж, швидкість перетворення змінюється

залежно від VBX. Якби

напруга в даному прикладі складала 0,18 В, перетворення зайняло лише половину

тактів у порівнянні з VBX = 0,37 В.

Рисунок 3.3

– Три типи АЦП: а) слідкувальний;

б) паралельний; в) послідовних

наближень

Максимальна тактова частота АЦП слідкувального типу залежить від затримки поширення сигналу

в ЦАП і компараторі. Після кожного тактового імпульсу вихід лічильника має бути

перетворений ЦАП, а результат перетворення з виходу потрапити на інверсний вхід

компаратора. Компаратор віднімає деяку частину часу для реакції на зміну VЦАП, створюючи новий сигнал

керування на додавання чи віднімання для реверсивного лічильника. Всі затримки

сигналу роблять слідкувальний АЦП найповільнішим з

усіх представлених типів АЦП. Слідкувальні АЦП

широкого поширення не отримали; серед інтегральних схем, що випускаються такими

фірмами, такими як Analog Devices,

Maxim, Burr-Brown, неможливо знайти слідкувальних АЦП. Треба відзначити, що АЦП послідовних

наближень працює з великою швидкодією з такою розрядністю слова. Проте

зустрічаються такі випадки, коли слідкувальний АЦП

буде корисним. Наприклад, якщо сигнал змінюється повільно відносно частоти

дискретизації, слідкувальний АЦП встановлюватиме

вихідне число за менше число тактів, ніж АЦП послідовних наближень.

Паралельний АЦП (рис. 3.3, б) – найшвидший з тих, що випускаються виробниками. Паралельний АЦП

містить по компаратору на кожен крок напруги. На один із входів кожного

компаратора подається вимірювана напруга. Інші входи компараторів підключаються

до лінійки резисторів. Якщо рухатися вгору по цій лінійці, то можна відмітити,

що кожен наступний компаратор підключений до вищої напруги з постійним кроком

приросту напруги. Залежно від зміни вхідної напруги будуть переключені у стан 1

лише ті компаратори, в яких було перевищено опорну напругу. Сигнали з виходів

всіх компараторів надходять в логічний блок – шифратор, який і задає вихідне

цифрове m-бітове слово АЦП залежно

від того, які компаратори в стані 0, а які в стані 1. Число компараторів

визначається числом кодових комбінацій 2m–1,

де m – роздільна здатність АЦП. Тоді для 3-бітового АЦП буде потрібно 7

компараторів, для 4-бітового – 15 компараторів і так далі. Роздільна здатність

паралельного АЦП лежить в межах, як правило, від 6 до 12 бітів. Нескладно

підрахувати, що для 6 бітного АЦП потрібно 63 вхідних компаратора.

Швидкість перетворення паралельного

АЦП складається з часу затримки одного компаратора і логічного блока.

Паралельні АЦП найбільш швидкодійні серед основних

типів АЦП. Їх швидкодія складає десяті частки мікросекунд. До недоліків

паралельних АЦП можна віднести різке збільшення вхідних компараторів разом з

збільшенням роздільної здатності. З цієї причини для них недосяжний бар’єр у 12

бітів, навіть з збільшенням міри інтегрування мікросхем. Такі величезні об’єми

інтегральних елементів (компараторів і шифраторів) в одній мікросхемі реально

впливають на робочі характеристики. Використання великого числа компараторів

веде до збільшення споживаного струму. Так, наприклад, 10-бітовий паралельний

АЦП може споживати струм до 0,5 А. У свою чергу, струм споживання визначає

потужність розсіювання корпусом мікросхеми, тому 8-12-бітові АЦП повинні мати на платі

ефективний тепловідвід від корпуса АЦП.

АЦП послідовного наближення (рис. 3.3, в) подібний до слідкувального АЦП в тому, що система ЦАП/лічильник формує

напругу, яка надходить на один вхід компаратора, а вхідний сигнал надходить на

інший вхід. Відмінність полягає в тому, що регістр послідовного наближення

виконує двійковий пошук, замість лічби вгору або вниз по одиниці. Візьмемо для

прикладу, що початкова вхідна напруга складає 3 В, а опорна – 5 В (див. рис. 3.3). Регістр

послідовного наближення виконає перетворення таким чином:

Встановити MSB, напруга на виході ЦАП дорівнює 2,5 В

Вихід компаратора – високий

логічний рівень, MSB залишається встановленим.

Результат: 1000 0000 Встановити біт 6, напруга на

виході ЦАП дорівнює 3,75 В (2,5 + 1,25)

Вихід компаратора - низький

логічний рівень, скидається біт 6.

Результат: 1000 0000 Встановити біт 5, напруга на

виході ЦАП дорівнює 3,125 В (2,5 + 0,625)

Вихід компаратора - низький

логічний рівень, скидається біт 5.

Результат: 1000 0000 Встановити біт 4, напруга на

виході ЦАП дорівнює 2,8125 В (2,5 + 0,312 5)

Вихід компаратора - високий,

залишається біт 4 встановленим.

Результат: 1001 0000 Встановити

біт 3, напруга на виході ЦАП рівна 2,968 В (2,8125 + 0,15625)

Вихід компаратора - високий,

залишається біт 3 встановленим.

Результат: 1001 1000 Встановити біт 2, напруга на

виході ЦАП дорівнює 3,04 В (2,968 + 0,078125)

Вихід компаратора - низький,

скидається біт 2.

Результат: 1001 1000 Встановити біт 1, напруга на

виході ЦАП дорівнює 3,007 В (2,8125 + 0,039)

Вихід компаратора - низький,

скидається біт 1.

Результат: 1001 1000 Встановити біт 0, напруга на

виході ЦАП дорівнює 2.988 В (2.8125 + 0.0195)

Вихід компаратора - високий,

залишається біт 0 встановленим.

Результат: 1001 1001

При використанні 8-бітового ЦАП

з вихідною напругою 0...5 В, цьому результату відповідає напруга, розрахована у

формулі 1.5.

2,5 + 0,3125

+ 0,15625 + 0,0195 = 2,988 В (1.5)

Це не точно 3 В, але настільки

близько, наскільки можна отримати з 8-бітовим перетворенням і опорною напругою

5 В.

8-бітовий АЦП послідовного

наближення може завершити перетворення за 8 тактів, незалежно від вхідної

напруги. Потрібно більше логічних кіл, ніж для слідкувального

АЦП, але швидкість перетворення буде вища.

АЦП подвійного інтегрування (рис. 3.4) використовує

інтегратор, за яким ставлять компаратор і лічильник. Вхід інтегратора підключається до вхідного

сигналу, і ємність інтегратора заряджається до рівня вхідної напруги тієї ж

полярності. Після певного числа тактів вхід інтегратора перемикається до

джерела опорної напруги (VREF1

на рис. 3.4), і ємність інтегратора

розряджається до величини цієї напруги. У той момент, коли ключ

замикається на VREF1,

лічильник відраховує стільки ж тактів, скільки займав час першого інтегрування.

Коли напруга на виході інтегратора падає нижче за величину другої опорної

напруги (VREF2 на рис. 3.4), вихід

компаратора переходить у стан високого логічного рівня, лічильник зупиняється,

а значення лічильника відповідає величині вхідної напруги. Більша вхідна

напруга дозволяє ємності інтегратора заряджатися до більшої величини протягом

часу первинного інтегрування, що приводить до більшого часу розрядження до VREF2, і до більшого

вихідного значення лічильника. Менше значення напруги на вході приводить до

меншого потенціалу на ємності інтегратора і, відповідно, до меншого вихідного

числа.

Рисунок 3.4

– АЦП подвійного інтегрування

Схема з подвійним інтегруванням

усуває проблеми точності синхронізації, оскільки один і той же генератор

тактових імпульсів застосовується для задання часу

заряду ємності і для приросту вмісту лічильника. Перетворювач з подвійним

інтегруванням витрачає відносно великий час на виконання перетворення, але

властива інтегратору фільтрація усуває шум.

3.4.1

Кодування вихідного слова

Наведені до цих пір приклади

базувалися на двійкових кодах, де кожен біт являв собою певну величину напруги,

відповідну вазі біта, а вся напруга

відповідала сумі ваг кожного одиничного біта у вихідному слові і була

величиною вхідної напруги. Основні типи АЦП подають вихідне слово в прямому

коді числа. Деякі АЦП подають вихідне слово в додатковому коді числа, де

негативна напруга має цифровий еквівалент у вигляді доповнення до двох прямого

коду числа. Деякі АЦП подають вихідне

слово в двійково-десятковому коді (Binary Coded Decimal, BCD). Але таке

подання простіше сприймається людиною, а

не обчислювальними машинами. Очевидно, що таке подання вимагає більшої

розрядності для даного діапазону; 12-бітовий двійковий вихід подаватиме

величини від 0 до 4095, а в двійково-десятковому 12-бітовому виході діапазон

величин зменшиться (0...3999). Даний код (BCD) використовується в АЦП з виходом

на цифрові індикатори.

3.4.2

Паралельний інтерфейс

АЦП, що випускаються

промисловістю, забезпечуються різними вихідними паралельними і послідовними

інтерфейсами для роботи з багатьма типами МК. Деякі ІС містять більше одного

інтерфейсу для забезпечення сумісності з якомога більшою кількістю МК.

ІС МАХ151 фірми MAXIM/Dallas є типовим 10-бітовим АЦП з 8-бітовим універсальним

периферійним паралельним інтерфейсом для зв'язку з МК. Як показано на рисунку

3.5, інтерфейс Мах151 містить 8 бітів даних, виходи сигналів: ![]() (chip select) – "вибір мікросхеми",

(chip select) – "вибір мікросхеми", ![]() (read strobe) – "строб-імпульс

читання",

(read strobe) – "строб-імпульс

читання", ![]() – "зайнято". Також Мах151

містить вбудований пристрій вибирання-зберігання (ПВЗ).

– "зайнято". Також Мах151

містить вбудований пристрій вибирання-зберігання (ПВЗ).

На спаді імпульсу на входах ![]() і

і ![]() ПВЗ переходить

у режим зберігання, і стартує аналого-цифрове перетворення. У більшості систем

вихід

ПВЗ переходить

у режим зберігання, і стартує аналого-цифрове перетворення. У більшості систем

вихід ![]() з'єднується з декодером адреси і тому сигнал на ньому переходить в низький

логічний рівень перед сигналом на вході

з'єднується з декодером адреси і тому сигнал на ньому переходить в низький

логічний рівень перед сигналом на вході ![]() . Як тільки перетворення почалося, АЦП встановлює сигнал на виводі

. Як тільки перетворення почалося, АЦП встановлює сигнал на виводі ![]() у низький

(активний) рівень. Вивід

у низький

(активний) рівень. Вивід ![]() залишається в низькому логічному рівні до тих пір, поки не

завершиться перетворення.

залишається в низькому логічному рівні до тих пір, поки не

завершиться перетворення.

На першій стадії роботи, яка в

специфікації фірми MAXIM називається режимом повільної пам'яті (Slow Memory Mode),

МК чекає, утримуючи ![]() і

і ![]() на низькому

рівні доки перетворення не завершиться. Максимальний час перетворення

для МАХ151 складає 2,5 мкс.

на низькому

рівні доки перетворення не завершиться. Максимальний час перетворення

для МАХ151 складає 2,5 мкс.

Друга стадія називається режим ПЗП (ROM-mode). На

цій стадії процесор виконує цикл читання, в якому ПВЗ переходить у режим

фіксації рівня, і АЦП починає перетворення. Під час цієї стадії МК зчитує

результати попереднього перетворення. Сигнал ![]() не використовується на стадії

читання даних. Замість цього вивід

не використовується на стадії

читання даних. Замість цього вивід ![]() з'єднується з виводами МК

"запит переривань" або "почерговий опит пристроїв" (polling) для індикації завершення перетворення. Коли рівень

з'єднується з виводами МК

"запит переривань" або "почерговий опит пристроїв" (polling) для індикації завершення перетворення. Коли рівень

![]() стає

високим, МК проводить наступне читання, щоб отримати наступний результат і

почати наступне перетворення. Хоча в специфікаціях (data

sheets) [11, 36] ці операції відносять до двох різних

стадій роботи, АЦП працює аналогічним чином в обох випадках:

стає

високим, МК проводить наступне читання, щоб отримати наступний результат і

почати наступне перетворення. Хоча в специфікаціях (data

sheets) [11, 36] ці операції відносять до двох різних

стадій роботи, АЦП працює аналогічним чином в обох випадках:

-

за спадом імпульсів на входах ![]() і

і ![]() починається цикл перетворення;

починається цикл перетворення;

-

поточний результат стає доступний на шині після того,

як закінчився час доступу читання;

-

поки ![]() і

і ![]() залишаються в стані низького логічного рівня,

поточний результат залишається доступним на шині;

залишаються в стані низького логічного рівня,

поточний результат залишається доступним на шині;

-

після завершення циклу перетворення дані перетворення

стають доступні процесору; якщо![]() і

і ![]() все ще залишаються в низькому рівні,

ці дані заміщають на шині результат попереднього перетворення.

все ще залишаються в низькому рівні,

ці дані заміщають на шині результат попереднього перетворення.

Рисунок 3.5 – Інтерфейс ІМС MAX151

3.4.3

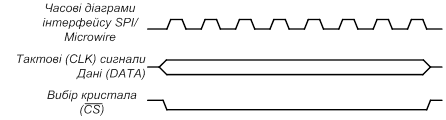

Послідовний інтерфейс SPI

Периферійний послідовний

інтерфейс SPI застосовується як для з’єднання МК між собою, так і МК з

периферійними пристроями. У одному сеансі зв'язку беруть участь лише 2

пристрої, з яких один обов'язково МК, а інший або МК, або периферійний пристрій

з інтерфейсом SPI (АЦП, датчик, пам'ять, виконавчий пристрій). У периферійному

послідовному інтерфейсі SPI використовуються цифрові сигнали "такти"

(clock), «вибір кристала (мікросхеми)» (chip select), "вхід

даних" (data input) і

"вихід даних" (data output),

але немає адресних сигналів. Дані зчитуються з виходу послідовного АЦП по біту

за такт (рисунок 3.6). Кожен з пристроїв, підключених до шини SPI, вимагає

наявності окремого сигналу ![]() , яким він вибирається. Два пристрої працюють в режимі

"ведучий-ведений".

, яким він вибирається. Два пристрої працюють в режимі

"ведучий-ведений".

Рисунок 3.6

– Шина SPI

Дані, які потрібно передати,

завантажуються в 8-бітові регістри портів і вхід даних ведучого пристрою

з'єднується з виходом даних веденого. У свою чергу, вихід даних ведучого

пристрою з'єднується з входом даних веденого. Також підключені до МК (ведучого

пристрою) останні вище перелічені ведені пристрої, які включаються за окремими

сигналами "вибір кристала". Хоча регістри мають по 8 бітів, але при такому підключенні входів і

виходів утворюється спільний 16-бітовий регістр зсуву і, крім того, одночасно

передаються по двох лініях дані в обох напрямах. Зсув проводиться тактовими

сигналами від тактового генератора ведучого пристрою.

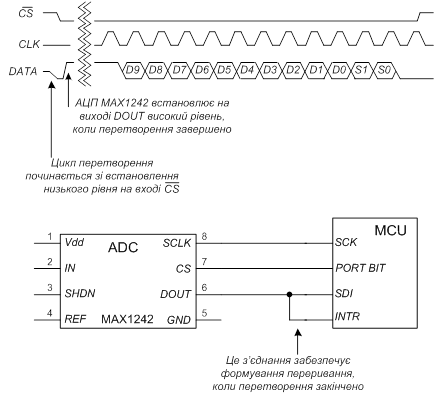

Рисунок 3.7

– Інтерфейс АЦП MAX1242

ІС МАХ1242 фірми MAXIM/Dallas є типовим прикладом АЦП з інтерфейсом SPI. MAX1242 –

10-бітний АЦП послідовного наближення з ПВЗ в одному 8-вивідному корпусі. На

рисунку 3.6 наведені часові діаграми роботи послідовного

інтерфейсу ІС МAX1242. За спадом сигналу ![]() починається перетворення, яке триває

максимум 7,5 мкс. Після завершення перетворення на виводі (data output) встановлюється

високий логічний рівень. Процесор потім може зчитати дані біт за бітом,

синхронізуючи читання сигналами "такти" на лінії тактових імпульсів (clock line) і керувати виведенням даних на виводах DOUT (data output) мікросхеми МAX1242. Після того, як 10 бітів даних

прочитані, ІС МАХ1242 формує два службових біти (sub-bits)

S1 і S0. Після проходження 13 тактів синхронізації ІС встановлює вихід в

0, що означає закінчення видачі даних з виводу DOUT (data output).

починається перетворення, яке триває

максимум 7,5 мкс. Після завершення перетворення на виводі (data output) встановлюється

високий логічний рівень. Процесор потім може зчитати дані біт за бітом,

синхронізуючи читання сигналами "такти" на лінії тактових імпульсів (clock line) і керувати виведенням даних на виводах DOUT (data output) мікросхеми МAX1242. Після того, як 10 бітів даних

прочитані, ІС МАХ1242 формує два службових біти (sub-bits)

S1 і S0. Після проходження 13 тактів синхронізації ІС встановлює вихід в

0, що означає закінчення видачі даних з виводу DOUT (data output).

На рисунку 3.7 показано, як АЦП

МAX1242 може бути з’єднаний з МК за допомогою вбудованого інтерфейсу SPI.

Сигнал SCLK з АЦП Мах1242 надходить на SCK

SPI МК, а вихід DOUT АЦП МАХ1242

з'єднується з SDI входом даних

МК. Один з виводів порту МК генерує сигнал ![]() для вибору ІС

МAX1242. Шина SPI буде недоступна для з'єднання з іншими периферійними

пристроями до тих пір, поки не закінчиться перетворення і не буде прочитаний

результат. Якщо є підпрограми обробки переривань, що використовують

SPI-пристрої, вони мають бути заборонені під час перетворення. Для уникнення

пов'язаних з перериваннями проблем АЦП МAX1242 міг би звертатися до МК за

допомогою спеціалізованої (нестандартної) SPI-шини. Такий підхід вимагає

використання додатково трьох виводів МК,

оскільки більшість МК якщо і мають, то лише один SPI-інтерфейс. Усі

необхідні часові діаграми спеціалізованої SPI-шини мають бути виконані

програмно і виведені на інший порт (вивід) МК.

для вибору ІС

МAX1242. Шина SPI буде недоступна для з'єднання з іншими периферійними

пристроями до тих пір, поки не закінчиться перетворення і не буде прочитаний

результат. Якщо є підпрограми обробки переривань, що використовують

SPI-пристрої, вони мають бути заборонені під час перетворення. Для уникнення

пов'язаних з перериваннями проблем АЦП МAX1242 міг би звертатися до МК за

допомогою спеціалізованої (нестандартної) SPI-шини. Такий підхід вимагає

використання додатково трьох виводів МК,

оскільки більшість МК якщо і мають, то лише один SPI-інтерфейс. Усі

необхідні часові діаграми спеціалізованої SPI-шини мають бути виконані

програмно і виведені на інший порт (вивід) МК.

Можна генерувати переривання МК

після того, як аналого-цифрове перетворення завершиться. Спеціальне з'єднання

для виконання такої функції показане на рисунку 3.7. Вивід DOUT АЦП МAX1242 з'єднується з виводом INTR ("переривання") МК. Коли на ![]() низький рівень і перетворення завершене, сигнал DOUT перейде у високий рівень, що викликає переривання на МК. Для

використання даного методу програмне забезпечення повинно заборонити або

ігнорувати переривання під час перетворення.

низький рівень і перетворення завершене, сигнал DOUT перейде у високий рівень, що викликає переривання на МК. Для

використання даного методу програмне забезпечення повинно заборонити або

ігнорувати переривання під час перетворення.

Іншим прикладом АЦП зі

SPI-інтерфейсом є MCAD7823 фірми Analog Devices. На відміну від

МAX1242, АЦП AD7823 не змінює логічний рівень на виводі даних, поки МК не почне

зчитувати результат, тому шина інтерфейсу SPI може використовуватися іншими

пристроями доки йде перетворення. Оскільки немає зміни рівня на виводі даних,

то немає й спеціального сигналу для МП про те, що перетворення завершилося.

Процесор сам повинен дати старт перетворенню, потім почекати деякий час до

завершення перетворення і, нарешті,

зчитати результат. Один з методів керування цим процесом – використання

регулярних переривань таймера. З кожним перериванням результат зчитується, і

починається нове перетворення.

3.4.4 Спеціалізовані послідовні інтерфейси

Типовий АЦП, що використовує інтерфейс I2C, – це ІС PCF8591 фірми Philips. Ця мікросхема

містить і АЦП, і ЦАП. ІС PCF8591 містить

три адресні виводи: А0, А1 і А2. Вони можуть бути з’єднані з високим або з

низьким рівнем для вибору пристрою, що адресується. Коли декодується адреса

периферійного пристрою, ІС PCF8591 відповідатиме на адресу 1001ххх, де ххх узгоджується з рівнями на А2, А1 і А0. Це дозволяє

розмістити до восьми мікросхем PCF8591 на одній I2C-шині.

DS2450 – чотириканальний

16-розрядний аналого-цифровий перетворювач послідовного наближення. Він містить

на вході високоімпендансний аналоговий комутатор, що

підключає по черзі, відповідно до

команд, що надходять по однопроводовому інтерфейсу, вхідні сигнали від

чотирьох аналогових датчиків на вхід АЦП. Рівень вхідних напруг сигналів може

бути встановлений програмно для двох діапазонів: 2,56 В або 5,12 В.

Роздільність приладу також програмується від 1 до 16 розрядів. Швидкість

перетворення становить близько 80 мкс/біт.

Максимальна швидкість передачі даних 16,3 Кбіт/с.

Як і всі прилади MіcroLAN, DS2450 містить ПЗП з унікальним серійним номером,

груповим кодом і контрольною сумою. "Паразитного" живлення вистачає

тільки на роботу в режимі зв'язку з мікроконтролером.

Для аналого-цифрового перетворення необхідне підключення шини до додаткового

джерела напруги 5 В або подача живлення на вивід Vcc (рисунок 3.8).

Рисунок 3.8 – Схема підключення DS2450 по шині 1-Wіre

Таблиця 3.5 – Сторінка

читання-перетворення (сторінка 0)

|

Адреса |

Біт 7 |

Біт 6 |

Біт 5 |

Біт 4 |

Біт 3 |

Біт 2 |

Біт1 |

Біт 0 |

|

00 |

А |

А |

А |

А |

А |

А |

А |

молодший біт |

|

01 |

старший

біт |

А |

А |

А |

А |

А |

А |

А |

|

02 |

В |

В |

В |

В |

В |

В |

В |

молодший біт |

|

03 |

старший

біт |

В |

В |

В |

В |

В |

В |

В |

|

04 |

С |

С |

С |

С |

С |

С |

С |

молодший біт |

|

05 |

старший

біт |

С |

С |

С |

С |

С |

С |

С |

|

06 |

D |

D |

D |

D |

D |

D |

D |

молодший біт |

|

07 |

старший

біт |

D |

D |

D |

D |

D |

D |

D |

Всі

регістри DS2450 розташовані в 24 сусідніх байтах і організовані у вигляді трьох

сторінок по 8 байтів. Перша сторінка (сторінка 0),

названа сторінкою читання-перетворення, містить область пам'яті, де

розташовуються результати аналого-цифрового

перетворення для наступного читання їхнім мікроконтролером.

Починаючи з молодшої адреси порту А, кожному порту відведено 16 бітів для

зберігання результату перетворення (таблиця 3.5). При подачі живлення в усі

регістри читання-перетворення за замовчуванням записуються нулі. Старший

значущий біт результату перетворення завжди перебуває на фіксованому місці,

незалежно від необхідної розрядності. При розрядності менше 16 бітів для

формування 16 бітового результату молодші значущі біти будуть доповнюватися

нулями. Якщо в конкретному випадку використовуються не всі чотири порти, то для

першого порту буде застосований вхід D, для другого – С й так далі. При цьому

мінімізується завантаження однопроводової шини й скорочується час перевірки правильності

передачі даних.

Керування портами й інформація

про стан цих портів розташована на сторінці 1 (табл. 3.6). Як і у випадку

сторінки читання-перетворення, на кожний порт відведено по 16 бітів. Чотири

молодших біти RC3-RC0 – двійкове подання числа перетворених бітів. Код 11112

формує 15-бітовий результат. У випадку повного 16 бітового перетворення повинен

бути код 00002.

Таблиця 3.6 – Сторінка керування

й стану портів (сторінка 1)

|

Адреса |

Біт 7 |

Біт 6 |

Біт 5 |

Біт 4 |

Біт 3 |

Біт 2 |

Біт 1 |

Біт 0 |

|

08 |

0Е-А |

0С-А |

0 |

0 |

RC3-A |

RC2-A |

RC1-A |

RC0-A |

|

09 |

POR |

0 |

AFH-A |

AFL-A |

АЕН-А |

AEL-A |

0 |

IR-A |

|

0А |

0Е-В |

0С-В |

0 |

0 |

RC3-B |

RC2-B |

RC1-B |

RC0-B |

|

0B |

POR |

0 |

AFH-B |

AFL-B |

АЕН-В |

AEL-B |

0 |

IR-B |

|

0С |

ОЕ-С |

ОС-С |

0 |

0 |

RC3-A |

RC2-A |

RC1-A |

RC0-A |

|

0D |

POR |

0 |

AFH-C |

AFL-C |

АЕН-С |

AEL-C |

0 |

IR-C |

|

0Е |

0E-D |

0C-D |

0 |

0 |

RC-3 |

RC2-D |

RC1-D |

RC0-D |

|

0F |

POR |

0 |

AFH-D |

AFL-D |

AEH-D |

AEL-D |

0 |

IR-D |

Біти 0С (керування виходом) і 0Е

(дозвіл виходу) керують роботою порту на вихід. При роботі порту як аналоговий

вхід (прийом даних) біт ОЕ повинен бути встановлений в "0", при цьому

стан біта 0С ігнорується. Якщо біт 0Е встановлений в "1", то при

встановленні 0С в "0" вихідний транзистор даного порту буде

відкритий, а при 0С=1 – замкнений. Наприклад, при підключенні

резистора навантаження на "плюс" живлення, біт 0С буде безпосередньо

перетворюватися в напругу, що еквівалентна його логічному стану.

За

допомогою біта ІR у другому байті керування й стану вибирається діапазон

вхідних напруг. Установлення ІR в "0" дозволяє одержати максимально

можливий результат перетворення при напрузі 2,2 В. При ІR = 1 одержання

такого ж результату можливо при вхідній напрузі 5,1 В. Бітами AEL і AEH

установлюється дозвіл відповіді приладу на команду "Умовного

пошуку" у випадку, коли результати перетворення

вищі (AEH) або нижчі (AEL) граничних значень. Прапорці AFL і AFH указують мікроконтролеру на перевищення встановлених порогів при останному перетворенні. Прапорці скидаються автоматично,

якщо результат нового перетворення не виходить за встановлені межі.

Біт POR (скидання після включення

живлення) автоматично встановлюється в "1" на весь час виконання

циклу скидання установок приладу при включенні живлення. Поки цей біт

установлений, прилад буде відповідати на команду "Умовного

пошуку" для того, щоб повідомити мікроконтролер про те, що дані керування й пороги не дійсні.

Після завершення циклу скидання біт POR скидається мікроконтролером.

Це може виконуватися одночасно з установленням даних керування й порогів, при

цьому мікроконтролер записує в POR "1". У

цьому випадку прилад відповідає на команду "Умовного

пошуку", але не генерує скидання.

Регістри граничних напруг кожного

порту розташовані на сторінці пам'яті 2, починаючи з молодшого біта нижнього

порога. При включенні живлення за замовчуванням установлюються: нижній поріг –

00h, верхній поріг – FFh. Розмір порогів завжди

становить 8 бітів. Коли дозвіл більше або дорівнює 8 бітів, то прапорець

перевищення порога буде встановлений, якщо 8 старших значущих біт результату

перетворення дають число, більше вмісту регістра AFH або менше вмісту регістра

AFL. При дозволі менше 8 бітів молодші значущі біти регістрів граничних напруг

ігноруються (сторінка 2 (табл. 3.7)).

Таблиця 3.7 – Сторінка

граничних значень (сторінка 2)

|

Адреса |

Біт 7 |

Біт 6 |

Біт 5 |

Біт 4 |

Біт 3 |

Біт 2 |

Біт 1 |

Біт 0 |

|

10 |

СБМБ |

А |

А |

А |

А |

А |

А |

МБМБ |

|

11 |

СБСБ |

А |

А |

А |

А |

А |

А |

МБСБ |

|

12 |

СБМБ |

В |

В |

В |

В |

В |

В |

МБМБ |

|

13 |

СБСБ |

В |

В |

В |

В |

В |

В |

МБСБ |

|

14 |

СБМБ |

С |

С |

С |

С |

С |

С |

МБМБ |

|

15 |

СБСБ |

С |

С |

С |

С |

С |

С |

МБСБ |

|

16 |

СБМБ |

D |

D |

D |

D |

D |

D |

МБМБ |

|

17 |

СБСБ |

D |

D |

D |

D |

D |

D |

МБСБ |

СБМБ

– старший біт молодшого байта; СБСБ – старший біт старшого байта; МБМБ –

молодший біт молодшого байта; МБСБ – молодший біт старшого байта

Аналого-цифрове

перетворення для одного або декількох портів виконується за командою

"Перетворення" (3Ch). Перетворення займає від 60 до 80 мкс на біт плюс час виходу (160 мкс)

після завершення команди перетворення. Наприклад, для чотирьох портів з

роздільністю 12 бітів час виконання команди перетворення складе

4×12×80 мкс +160 мкс

= 4 мс. Якщо DS2450 підключений до зовнішнього

джерела живлення через вивід Vcc, то мікроконтролер в цей час

може працювати з іншими приладами мережі. У випадку живлення приладу від

однопроводової шини мікроконтролер не може

зв'язуватися з іншими приладами, тому що він повинен забезпечити живлення

DS2450 на весь час перетворення.

Деякі АЦП оснащені своїм власним

інтерфейсом. Типовим прикладом є ІС АЦП МAX1101 фірми MAXIM/Dallas

. Це 8-бітовий АЦП, що призначений для роботи з приладами із зарядовим зв'язком

(ПЗЗ). АЦП МAX1101 для забезпечення

інтерфейсу використовує 4 виводи: MODE ("режим роботи"), LOAD

("навантаження"), DATA ("дані") і SCLK ("такти").

Сигнал на виводі MODE визначає, записуються чи зчитуються дані (1 – читання, 0

– запис). Вивід DATA – двонаправлений, сигнал SCLK

синхронізує дані, що зчитуються або записуються в пристрій, а вивід LOAD

використовується після процедури запису для синхронізації запису даних у

внутрішні регістри. Синхронний послідовний інтерфейс ІС МAX1101 подібний до

SPI, але, оскільки відсутній сигнал "вибір кристала" (chip select), на шині не може

бути використано багато периферійних пристроїв. Кожен АЦП МAX1101 потребує

чотирьох ліній зв'язку з МП.

Проблема використання будь-якого послідовного

інтерфейсу для АЦП в тому, що послідовний інтерфейс обмежує швидкість

перетворення. Окремі види послідовних інтерфейсів вносять додаткові часові

обмеження. Оскільки прилади обмінюються даними по шині I2C розрядністю слова, принаймні, 20 бітів, 1-Ware, I2C-пристрій не в змозі досягти

швидкості, подібний SPI-пристрою. З цієї

причини випускається набагато більше АЦП з інтерфейсом SPI, ніж I2C.

Необхідна пропускна

здатність послідовного інтерфейсу диктує умови вибору інтерфейсу. Якщо

необхідно досягти швидкості перетворення 100000 вибірок/с по 8 бітів при

використанні програмно сформованого SPI-інтерфейсу, тоді слід врахувати, що МК

не зможе витратити більш ніж 1/(100000×8), або 1,25 мкс,

на кожен біт. Може виявитися неможливим виконання процесором яких-небудь інших

операцій, після чого перевага може буде надана АЦП з паралельним інтерфейсом

або МК з апаратною підтримкою SPI.

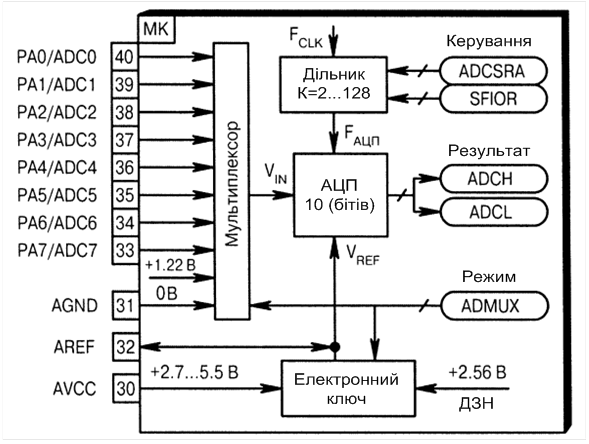

3.5 Вбудований

АЦП мікроконтролерів AVR

На рисунку 3.9 як приклад наведена структурна

схема модуля АЦП, що застосовується

в МК Atmel ATmega16-16PU.

Перетворення "аналог-цифра" здійснюється в

10-бітовому АЦП послідовного наближення. Для його нормальної роботи потрібно

три сигнали: вхідний VIN, тактовий FАЦП, зразковий VREF.

Сигнал VIN поступає від мультиплексора,

що комутує вісім аналогових каналів з ліній РА0...РА7 та дві тестових напруги 0 і +1,22В. Вибір джерела

сигналу здійснюється програмним способом через регістр ADMUX. Сигнал FАЦП

виходить з тактового сигналу FCLK шляхом ділення на коефіцієнт

2...128, що програмно задається регістром ADCSRA. Усередині блоку АЦП

частота FАЦП ділиться ще раз на 13 або 14 залежно від

одноразового або безперервного режиму вимірів. Це і буде істинним значенням

частоти дискретизація сигналу Fд.

Рисунок 3.9 – Структурная схема модуля АЦП в МК Atmel ATmega16.

Приклад. Нехай

FCLK = 8 МГц, коефіцієнт ділення встановлений 16, відповідно,

FAЦП = 500 кГц, Fд = 38,5 кГц (13тактів) або Fд= 35,7 кГц (14тактів).

Сигнал VREF може поступати з трьох

напрямів: від вхідної лінії AREF, від внутрішнього джерела зразкової напруги +2,56 В,

від джерела живлення AVCC. Перемикання здійснюється електронним ключем, який керується регістром

ADMUX. Вивід AREF має безпосередній електричний зв'язок з модулем АЦП, тому,

для зменшення наведень, його шунтують керамічним

конденсатором ємністю 0,1 мкФ.

Результат кожного вимірювання поміщається в регістри ADCH (старші 2 біта)

і ADCL (молодші 8 бітів). Разом в двох

регістрах утворюється число

в діапазоні 0... 1023. Ціна одного ділення – VREF/1024.

Це

справедливо для "чистого" режима 10 біт. У ATmega

16 є ще один режим, що умовно називається 8/10 біт. У ньому вимірювання

проводиться з точністю 10 бітів, але відображаються усього лише 8 старших

бітів, тобто діапазон складає 0...255, ціна одного ділення VREF/256.

При роботі АЦП потрібно на початку програми відключати

вхідні "pull-up" резистори, оскільки лінії ADC0...ADC7 за

сумісництвом ще є цифровими входами РА0...РА7.

Конфігурація джерела

Сигнал в АЦП подається через мультиплексор,

з одного з восьми (у кращому разі, часто буває менше) входів. Вибір входу

здійснюється регістром ADMUX, а

точніше його бітами MUX3– MUX0.

Записане туди число визначає вхід.

Наприклад, якщо MUX3.0 = 0100, то підключено вхід ADC4.

Крім того, існує декілька службових комбінацій бітів

MUX, що використовуються для калібрування. Наприклад, 1110 підключає до АЦП

внутрішнє джерело опорної напруги на 1.23 вольта. А якщо записати в MUX3.0 усі одиниці,

то АЦП буде зсередини посаджено на землю. Це корисно для виявлення різних шумів

і перешкод.

Вибір опорного сигналу

Ця максимальна напруга, яка буде узята за максимум при

вимірах. Опорна напруга має бути як можна стабільніша, без перешкод і коливань –

від цього кардинальним чином залежить точність роботи АЦП. Задається вона бітами

REFS1.0 регістра ADMUX.

По дефолту там стоїть REFS1.0 = 00 – зовнішнє ДЗН, що підключено

до входу AREF.

REFS1.0 = 01– береться напруга живлення з входу AVCC. Подавати туди плюс живлення

бажано через LC фільтр, щоб не було спотворень.

REFS1.0 = 11 – внутрішнє джерело опорної напруги на 2,56

вольт.

Швидкість роботи АЦП

Частота вибірки АЦП задається у бітах переддільника ADPS2.0

регістра ADCSR. Найоптимальніша

точність роботи модуля АЦП знаходиться в межах 50–200кГц, тому переддільник варто настроювати виходячи з цих міркувань. З

підвищенням частоти точність падає.

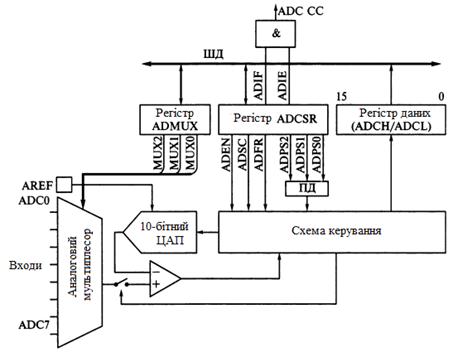

Переривання

У АЦП є переривання по закінченню перетворення. Його можна

дозволити бітом ADIE. Прапор ADIF (регістр

ADCSR) автоматом знімається при виході

на вектор переривання по АЦП.

Дані з АЦП потрапляють

в регістрову пару ADCH : ADCL звідки їх можна забрати. Регістрова пара

16ти розрядна, а АЦП має розрядність 10біт. У результаті, лише один регістр

зайнятий повністю, а другий займає два біти, що лише залишилися. Так от,

вирівнювання може бути як по правому краю - старші два біти в ADCH, а молодші в

ADCL, або по лівому - старші біти в ADCH, а два молодших біта в ADCL.

[x][x][x][x][x][x][9][8]:[7][6][5][4][3][2][1][0]

або [9][8][7][6][5][4][3][2]:[1][0][x][x][x][x][x][x]

Робимо вирівнювання по лівому краю. Беремо старші розряди тільки з регістра ADCH, а

молодші не враховуємо. Разом, число відліків стає 256. За вирівнювання

відповідає біт ADLAR в регістрі ADMUX

0 - вирівнювання по правій межі, 1 - по лівій.

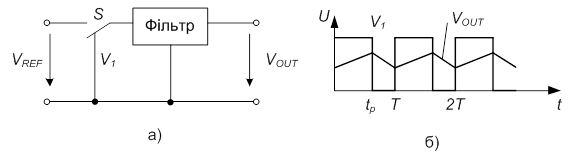

Запуск перетворення в ручному або безперервному режимі

Для запуску перетворення треба спочатку дозволити

роботу ADC, установкою біта ADEN в

регістрі ADCSR і в тому ж регістрі

встановити біт ADSC. Для запуску

безперервного перетворення (одне за іншим) треба також встановити біт ADFR

в регістрі ADCSR

Рисунок

3.10 – Схема аналого-цифрового

перетворювача мікроконтролерів AVR