Архітектура МПС. Структура та

функціонування МПС

1 Архітектура мікропроцесорної системи

2 Структура та функціонування мікропроцесорної системи

3 Архітектура мікропроцесора i8085

1 Архітектура мікропроцесорної системи

Поняття архітектури

мікропроцесора визначає його складові частини, а також зв'язки та взаємодію між

ними. Архітектура містить: 1) структурну схему самого МП; 2) програмну модель

МП (опис функцій регістрів); 3) інформацію про організацію пам'яті (ємність

пам'яті та способи її адресації); 4) опис організації процедур

введення-виведення.

Існують два основних типи

архітектури мікропроцесорної системи – фоннейманівська та гарвардська. Структурні схеми обох архітектур містять:

процесорний елемент, пам'ять, інтерфейси введення-виведення (ІВВ) і пристрої введення-виведення

(ПВВ). Пам'ять і ІВВ для різних типів МП можуть бути як внутрішніми (розміщуватися на тому ж кристалі, що і

процесорний елемент), так і зовнішніми. Процесорний елемент містить регістри,

арифметико-логічний пристрій (АЛП), пристрій керування і виконує функції

обробки даних та керування процесами обміну інформацією. Пам'ять забезпечує

зберігання кодів команд програми і даних. Інтерфейси призначені для зв'язку з

ПВВ (наприклад, з клавіатурою, дисплеєм, принтерами, датчиками інформації).

Усі елементи структурної схеми з'єднані за допомогою шин.

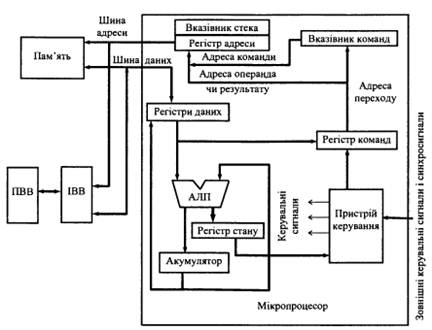

Рисунок 1 – Структурна схема з процесором фоннейманівської

архітектури

Розширену структурну схему

МПС з процесором фоннейманівської архітектури наведено на рисунку 1.

Схема процесора містить

пристрій керування, АЛП, регістри: адреси, даних, команд, стану, акумулятор,

лічильник команд та вказівник стека.

Пристрій керування відповідно до кодів команд та

зовнішніх сигналів керування і сигналів синхронізації виробляє сигнали керування

для всіх блоків структурної схеми МП, а також керує обміном інформацією між МП,

пам'яттю і ПВВ. Пристрій керування реалізує такі функції:

1. Функція початкового

встановлення МП. Зовнішній сигнал початкового встановлення процесора RESET формується

при ввімкненні джерела живлення МП або при натисканні кнопки RESET. У

разі появи цього сигналу пристрій керування забезпечує завантаження нульового

значення у програмний лічильник, що

ініціює вибірку з пам'яті байта команди з нульовою адресою. Наприкінці вибірки

вміст лічильника команд збільшується на одиницю і вибирається байт команди з

наступною адресою. Таким чином виконується вся записана у пам'яті програма.

2. Функція синхронізації.

Згідно із зовнішніми сигналами керування і сигналами синхронізації пристрій

керування синхронізує роботу всіх блоків МП.

3.

Функція переривань. Із надходженням сигналу переривання пристрій керування

ініціює роботу підпрограми обробки відповідного переривання. Потреба у

реалізації функцій переривань виникає тоді, коли під час виконання основної

програми треба перевести МП на розв'язання іншої задачі, наприклад, обробки

аварійної ситуації або роботи з ПВВ.

4. Функція узгодження

швидкодії модулів мікропроцесорної системи. Під час обслуговування пам'яті та

ПВВ із значно меншою швидкодією, ніж МП, узгодження швидкодії вирішується

генерацією тактів очікування МП, а під час обслуговування пристроїв з більшою

швидкодією, ніж МП, використовується режим безпосереднього доступу до пам'яті.

Арифметико-логічний пристрій являє собою комбінаційну

схему на основі суматора, який сигналами з виходів пристрою керування налагоджується

на виконання певної арифметичної або логічної операції: додавання, віднімання,

І, АБО, НЕ, виключне АБО, зсув, порівняння, десяткова корекція. Отже, АЛП

виконує арифметичні або логічні операції над операндами, які пересилаються з

пам'яті і/або регістрів МП. Одержаний після виконання команди в АЛП результат

пересилається в регістр або комірку пам'яті.

Регістри призначені для зберігання n-розрядного двійкового числа. Вони являють собою п тригерів

зі схемами керування читанням/записом та вибірки. Регістри створюють внутрішню

пам'ять МП і використовуються для зберігання проміжних результатів обчислень.

Акумулятор – це регістр, у якому

зберігається один з операндів. Після виконання команди в акумуляторі замість

операнда розміщується результат операції.

Вказівник команду або програмний лічильник, призначений

для зберігання адреси комірки пам'яті, яка містить код наступної команди.

Програму дій МП записано в пам'яті у вигляді послідовності кодів команд. Для

переходу до наступної команди вміст лічильника збільшується на одиницю у

момент вибирання команди з пам'яті. Наприкінці виконання команди в лічильнику

команд зберігається адреса наступної команди.

Вказівник стека – це регістр, який зберігає

адресу останньої зайнятої комірки стека. Стеком або стековою пам'яттю

називається область пам'яті, організованої за принципом «останній прийшов –

перший пішов».

Регістр команд зберігає код

команди протягом усього часу виконання команди.

Регістр адреси і регістри

даних призначені для зберігання адрес і даних, які використовуються під час

виконання поточної команди у МП.

Регістр стану або регістр

прапорців (ознак) призначений для зберігання інформації про результат операції в АЛП і

являє собою декілька тригерів, які набувають одиничних або нульових значень.

2 Структура

та функціонування мікропроцесорної системи

На рисунку 2 наведена

структурна схема мікропроцесорної системи з МП, яка має шину адреси/даних, що

мультиплексується. Лінії A15-А8 є адресними, через них у систему передається

старший байт 16-розрядної адреси. У цю шину включений формувач (буферний

регістр ИР82) з постійно відкритим входом дозволу EN, що забезпечує роботу шини

на навантаження. Власної навантажувальної здатності у виводів МП, як правило,

недостатньо. Лінії AD7-0

мультиплексуються. Спочатку вони передають молодший байт адреси, ознакою чого

служить наявність сигналу ALE (Address Latch Enable), що завантажує цей байт у

регістр ИР82.

Після завантаження регістра

сигнал ALE знімається, і вміст регістра залишається незмінним аж до нового

завантаження в наступному циклі роботи процесора. Так формується 16-розрядна

шина адреси, що містить адресу A15-0. Ця адреса використовується блоками

постійної (ROM) й оперативної пам'яті

(RAM). Адресація портів введення і виведення даних вимагає восьми

розрядної адреси, що надає можливість працювати

не більш ніж з 256 портами кожного з типів. Адресу портів можна знімати

з будь-якої половини адресної шини.

Після передачі молодшого

байта адреси шина AD7-0 віддається для передачі даних. Напрямок передачі

задається буфером даних BD у залежності від сигналу Т (Transіt). При активному стані сигналу читання

RD (Read) дані передаються до мікропроцесора, при пасивному – у зворотному

напрямку. До шини даних підключені інформаційні виводи всіх модулів МПС.

Рисунок 2 –

Структура мікропроцесорної системи.

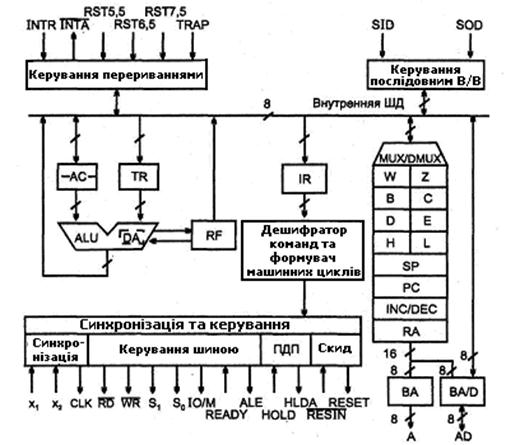

3 Архітектура мікропроцесора i8085

Архітектура мікропроцесора i8085 (К1821ВМ85А) наведена на рисунку

3. Мікропроцесор має восьми розрядну шину даних (внутрішню), через яку його

блоки обмінюються інформацією.

На схемі прийняті такі позначення:

- AC (Accumulator) – регістр-акумулятор,

виконаний на двоступінчастих тригерах і здатний зберігати одночасно два слова

(один з операндів і результат операції);

- TR (Temporary Register) – регістр тимчасового

зберігання одного з операндів;

- ALU (Arithmetic-Logic Unit) – арифметико-логічний пристрій, що виконує дії

над двома словами - операндами, які подаються на його входи. Акумулятор служить джерелом і приймачем даних, TR

- джерелом слова даних, збереженим на час виконання операції. АЛП функціонує відповідно до співвідношення А: =

А* В, де В зберігається в TR, другий операнд надходить від акумулятора, у нього

ж надходить результат операції. АЛП

безпосередньо виконує лише операції додавання, віднімання, зсуву, порівняння

слів, порозрядні логічні операції (кон’юнкцію, диз'юнкцію, додавання по модулю

2). Більше складні операції

(множення, ділення і ін.) виконуються у підпрограмах. У АЛП є схема переводу двійкових чисел у

двійково-десяткові (DA, Decimal Adjust);

- RF (Register Flags) – регістр

прапорців вказує ознаки результатів арифметичних або логічних операцій,

виконаних у АЛП.

Рисунок 3 – Архітектура мікропроцесора К1821ВМ85А

Існує п'ять ознак: Z (Zero) - нульовий результат, С

(Carry) - перенос, AC (Auxiliary Carry) - допоміжний перенос, S (Sign) - знак,

Р (Parity) - парність ваги слова. Ознака допоміжного переносу (переносу між молодшою

й старшою тетрадами восьми розрядного слова) потрібна при виконанні операцій у

двійково-десятковому коді. Ознаки служать для керування ходом процесу обробки

інформації.

Блок регістрів

Із внутрішньою шиною даних через мультиплексор

зв'язаний блок регістрів, частина яких спеціалізована, інша частина – регістри

загального призначення (РЗП) програмно доступні й можуть бути використана за

розсудом програміста. Регістри позначені через W,

Z, В, С, D, E, H, L, SP і PC. Регістри W і Z призначені тільки для тимчасового

зберігання даних під час вибірки команди з пам'яті й недоступні для

програміста.

Регістри В, С, D, Е, Н, L відносяться до регістрів загального призначення Ці

восьми розрядні регістри можуть застосовуватися або окремо, або у вигляді пар

ВС, DE, HL, що грають роль 16-розрядних регістрів. Пари регістрів мають назви В,

D, Н. Пара H, як правило, використається для розміщення в ній адрес при

непрямій регістровій адресації. У блоці регістрів є також 16-розрядні регістри SP

і PC. Регістр SP (Stack Pointer) – покажчик стека. Порядок уведення слів у стек і

їхнього зчитування визначені його пристроєм. При організації типу LIFO

(Last In - First Out) останнє записане в стек слово при зчитуванні з'являється

першим.

Операції зі стеком - PUSH

(запис слова) і POP (зчитування слова).

Апаратно стек реалізується у ОЗП, де для нього

виділяється певна область. Покажчик стека SP містить адресу останнього

зайнятого осередку. При виконанні операцій Push і Pop значення SP зменшується або

збільшується.

Програмний лічильник PC (Program Counter) дає

адресу команди, і може звертатися в кожний з 64К осередків АП. При скиданні МП PC приймає

нульовий стан, що, таким чином, є адресою першої команди, що виконується. Довжина команди становить

1...3 байта. Уміст програмного лічильника після вибірки чергового байта з

пам'яті автоматично інкрементується, так що в PC з'являється адреса наступної

команди, якщо поточна команда була однобайтовою, або наступного байта поточної

команди в противному випадку. Другий і третій байти команди надходять у регістри

W і Z, які не адресуються програмою й використаються тільки блоком внутрішнього

керування.

Схема INC/DEC (Increment/Decrement) змінює передані через неї слова на +1 або

-1.

Регістр команд IR (Instruction Register) приймає з

пам'яті перший байт команди, що після декодування створює сигнали, необхідні

для реалізації машинних циклів, запропонованих кодом операції.

Блок синхронізації й керування використає вихід дешифратора

команд і шифратора машинних циклів для синхронізації циклів, генерації сигналів

стану й керування шиною (зовнішніми пристроями мікропроцесорної системи).

При обміні між МП і пам'яттю або ЗП адреса

відповідної комірки пам'яті або ЗП від обраної команди або однієї з регістрових

пар передається у регістр адреси RA.

Буфер адреси ВА із трьома станами виходу видає

сигнали старших розрядів адреси на лінії адресної шини А15-8.

Буфер

шини адрес/даних BA/D із трьома станами виходу передає на шину A/D з поділом у

часі молодший байт адреси або байт даних.

МП, почавши роботу, вибирає з пам'яті й виконує одну команду за

іншою, поки не дійде до команди "Зупинка" (HLT). Мікропроцесор К1821 має такі

типи машинних циклів:

1. Вибірка команди (OF, Opcode

Fetch).

2. Читання з пам'яті (MR, Memory

Read).

3. Запис до пам'яті (MW, Memory

Write).

4. Читання з ЗП (IOR, Input-Output

Read).

5. Запису у ЗП (IOW, Input-Output

Write).

6. Підтвердження переривання (INA,

Interrupt Acknowledge).

7. Звільнення шин (BI, Bus Idle).

8. Зупинка (HALT).

На початку кожного машинного циклу генеруються

сигнали стану, які ідентифікують тип циклу й діють протягом усього циклу.

Функції виводів і сигналів:

- A15-8 – вихідні

лінії із трьома станами для видачі старшого байта адреси пам'яті або повної

адреси ЗП.

Переходять у третій стан у режимах HOLD, HALT і RESET;

- AD7-0 – двохнаправлені

мультиплексовані лінії із трьома станами для видачі молодшого байта адреси пам'яті або

повної адреси ЗП

в першому такті машинного циклу, після чого використовуються як шина даних;

- ALE – строб дозволу

завантаження молодшого байта адреси пам'яті в зовнішній регістр для його

зберігання протягом машинного циклу. З'являється у першому такті машинного циклу. Регістр завантажується спадом

сигналу ALE;

- ![]() ,

, ![]() –

строби читання або запису. Низький рівень відповідного сигналу інформує про те,

що адресована комірка пам'яті або зовнішній пристрій повинні виконати операцію

читання або запису. Виводи

переходять у третій стан у режимах HOLD, HALT і RESET;

–

строби читання або запису. Низький рівень відповідного сигналу інформує про те,

що адресована комірка пам'яті або зовнішній пристрій повинні виконати операцію

читання або запису. Виводи

переходять у третій стан у режимах HOLD, HALT і RESET;

- READY – вхідний сигнал, який

показує, що пам'ять або ЗП готові до обміну із МП. Якщо готовності пам'яті або ЗП

немає, МП входить у стан очікування, що може тривати будь-яке число тактів аж

до появи одиничного рівня сигналу READY;

- S1, S0 – сигнали стану МП, які

повідомляються зовнішньому середовищу. Формуються на початку й зберігаються під

час усього машинного циклу;

- IO/М – сигнал вибору пам'яті

або зовнішнього пристрою. При високому рівні відбувається звертання до ЗП, при

низькому – до пам'яті.

Разом із сигналами S1S0 сигнал IO/М ідентифікує тип

машинного

циклу. Сигнали стану й керуючі сигнали ![]() ,

, ![]() і

і ![]() для

різних машинних циклів мають наступні значення:

для

різних машинних циклів мають наступні значення:

Таблиця 1 – Сигнали стану та керування для різних машинних циклів

|

Тип МЦ |

Сигнали стану |

Сигнали керування |

||||

|

IO/М |

S1 |

S0 |

|

|

|

|

|

OF |

0 |

1 |

1 |

0 |

1 |

1 |

|

MR |

0 |

1 |

0 |

0 |

1 |

1 |

|

MW |

0 |

0 |

1 |

1 |

0 |

1 |

|

IOR |

1 |

1 |

0 |

0 |

1 |

1 |

|

IOW |

1 |

0 |

1 |

1 |

0 |

1 |

|

INA |

1 |

1 |

1 |

1 |

1 |

0 |

|

BI |

Z |

X |

X |

1 |

1 |

1 |

|

HALT |

Z |

0 |

0 |

Z |

Z |

1 |

·

X1, X2 – ці виводи призначені

для підключення кварцового резонатора або інших кіл, для забезпечення роботи

внутрішнього генератора синхроімпульсів МП. Частота на виводах у 2 рази

вище робочої частоти;

·

![]() (

(![]() ) –

вхід сигналу скидання МП у початковий стан. Сигнал може надійти у

будь-який час за командою оператора. Автоматично формується з подачею живлення. Під його впливом скидаються

регістри PC і IR, тригери дозволу переривання, підтвердження захоплення;

) –

вхід сигналу скидання МП у початковий стан. Сигнал може надійти у

будь-який час за командою оператора. Автоматично формується з подачею живлення. Під його впливом скидаються

регістри PC і IR, тригери дозволу переривання, підтвердження захоплення;

·

CLK – вихід синхроімпульсів для мікропроцесорної

системи. Частота цих імпульсів у два рази нижче частоти на виводах X1

і X2.

·

RESET – вихідний сигнал скидання для зовнішніх

модулів системи, прив'язаний до тактових імпульсів CLK (відрізняється від

сигналу RESIN по фазі);

·

INTR (Interrupt Request) – вхід запиту векторного

переривання, що викликає генерацію строба ![]() , якщо переривання дозволене

програмою. Адреса

підпрограми, що викликається цим входом, видається зовнішнім пристроєм. При скиданні прийом сигналу забороняються

(переривання заборонені);

, якщо переривання дозволене

програмою. Адреса

підпрограми, що викликається цим входом, видається зовнішнім пристроєм. При скиданні прийом сигналу забороняються

(переривання заборонені);

·

![]() (Interrupt

Acknowledge) – вихід строба підтвердження векторного переривання після

завершення поточного командного циклу.

Використовується для читання вектора переривання;

(Interrupt

Acknowledge) – вихід строба підтвердження векторного переривання після

завершення поточного командного циклу.

Використовується для читання вектора переривання;

·

RST 5,5; RST 6,5; RST 7,5 – входи запитів

радіального переривання типу RSTn (n = 5,5; 6,5; 7,5). Пріоритети фіксовані, вищий

пріоритет у входу RST 7,5. Пріоритети всієї групи запитів вище пріоритету

запиту INTR;

·

TRAP – вхід запиту переривання, що не маскується та

має максимальний пріоритет;

·

SID, SOD (Serial Input Data, Serial Output Data) –

вхід і вихід послідовної передачі даних;

·

HOLD

– сигнал запиту захоплення шин. Формується зовнішнім пристроєм;

·

HLDA – сигнал підтвердження захоплення (Hold Acknowledge).

Є відповіддю на сигнал HOLD, який формується наприкінці поточного машинного

циклу. Інформує о відключенні МП від системних шин. При цьому

шини й лінії керуючих сигналів ![]() ,

, ![]() , IO/М , ALE переводяться у третій

стан.

, IO/М , ALE переводяться у третій

стан.