Організація багато кристальної пам'яті

1

Проектування схем підключення мікросхем пам'яті

2

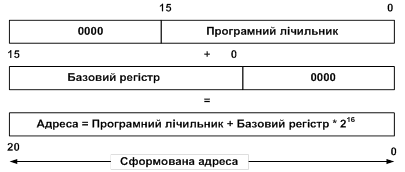

Способи розширення адресного простору мікропроцесора

2.1

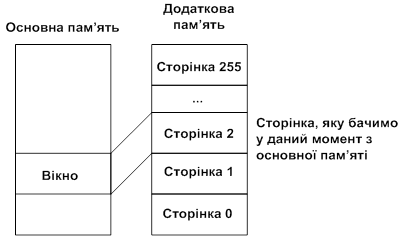

Метод сторінкового розширення адресного простору

2.2

Метод сегментного розширення адресного простору

2.3

Метод розширення адресного простору за допомогою вікон

1

Проектування схем підключення мікросхем пам'яті

При проектуванні схем підключення мікросхем пам'яті до

мікропроцесора розв’язуються такі задачі:

·

розробка схем адресації пам'яті і формування сигналів керування

на функціонально-логічному рівні;

·

аналіз навантажувальних умов в отриманій схемі,

забезпечення робочих режимів для виходів з відкритим колектором (стоком) і

застосування при необхідності буферних елементів для усунення перевантажень

джерел сигналів;

·

узгодження часових діаграм мікропроцесора і мікросхем

пам'яті.

При адресації пам'яті розміщають адреси постійних і

оперативних запам’ятовувальних пристроїв в заданих областях адресного простору.

Приклад 1

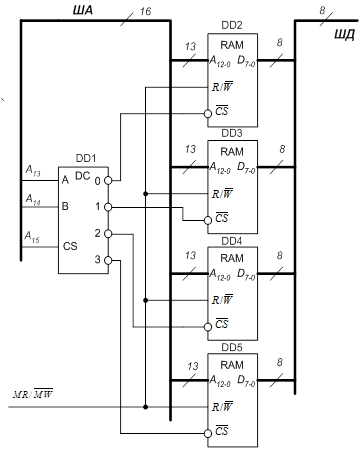

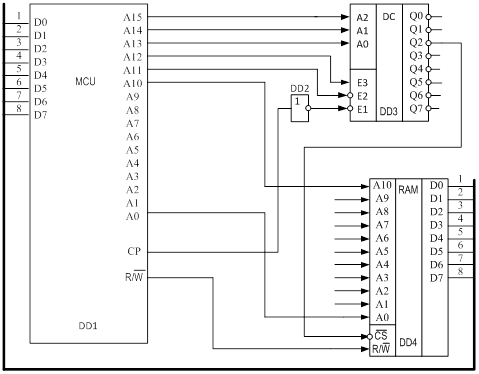

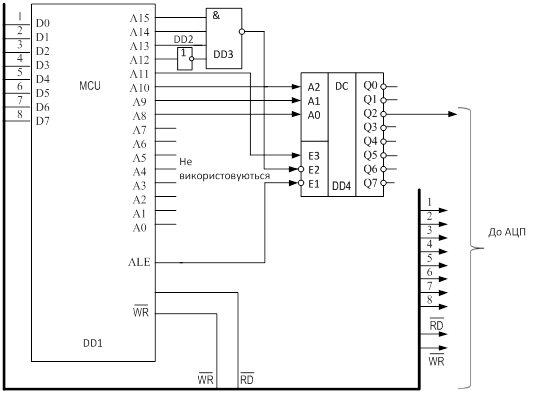

Рисунок 1 –

Схема підключення модуля пам’яті

Послідовність

дій мікропроцесора:

1.

Мікропроцесор (МП) поміщає адресу пам’яті на виводи адреси А15–А0.

2.

МП формує сигнал R/W, який інформує модуль

пам’яті о режимі роботи (1 – READ,

0 – WRITE).

3.

П’ять старших біт

адреси керують входом дозволу роботи модуля пам’яті (![]() ).

).

4.

Решта 11 біт адреси

поступають на модуль пам’яті. Модуль DD4 використовує

їх для вибірки конкретної комірки всередині мікросхеми, доступ до якої запитує

МП.

Необхідно:

Визначте організацію та об’єм ОЗП

1.

Намалюйте адресний простір МПС та показати де розташований модуль ОЗП.

2.

Визначте, який діапазон шістнадцятирічних адрес може активізувати модуль ОЗП.

3.

визначити чи можуть шістнадцятирічні адреси 607F, 57FA, 5F00, 15D0, AFF3 активізувати модуль пам’яті, і якщо так, то які з них.

4.

наведіть схему керування модулями ОЗП , якщо початковий об’єм ОЗП збільшений у два рази.

Приклад 2

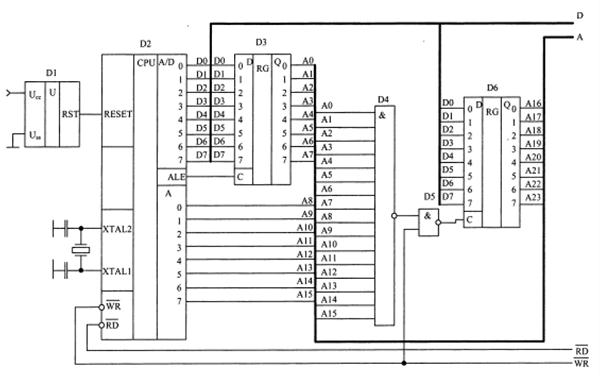

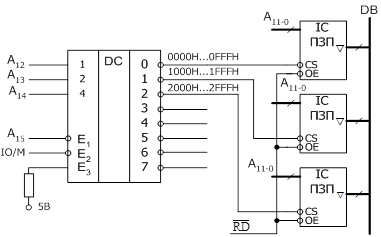

Рисунок

2 – Схема підключення АЦП до мікропроцесорної системи

На

рисунку 2 показаний один з способів реалізації логіки дешифрації

адреси. Сигнал вибору мікросхеми ![]() ,

який активізує АЦП, знімається з 8 старших ліній шини адреси мікропроцесора.

Якщо МП потрібно обмінятися інформацією з АЦП, то він видає на шину адресу, а

логіка дешифрації адреса переводить сигнал

,

який активізує АЦП, знімається з 8 старших ліній шини адреси мікропроцесора.

Якщо МП потрібно обмінятися інформацією з АЦП, то він видає на шину адресу, а

логіка дешифрації адреса переводить сигнал ![]() в стан з низьким рівнем напруги.

Необхідно: а) визначити адресу АЦП; б) змінити схему таким чином, щоб АЦП мав

адресу E8XXh, в) змінити

схему таким чином, щоб АЦП мав адресу FFXXh

в стан з низьким рівнем напруги.

Необхідно: а) визначити адресу АЦП; б) змінити схему таким чином, щоб АЦП мав

адресу E8XXh, в) змінити

схему таким чином, щоб АЦП мав адресу FFXXh

Приклад 3

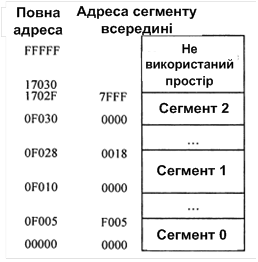

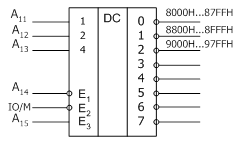

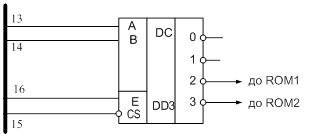

Типовим елементом схем адресації є дешифратор, у якому

використовуються як інформаційні, так і

входи дозволу. На рисунку 3 наведена

схема адресації ПЗП, яка складається з

трьох субмодулей з організацією 4Кх8. Адреси займають

12К у верхній частині АП, тобто зону від 0000Н до 2FFFH.

![]()

![]() Сигнал

дозволу роботи дешифратора Е = Е1Е2Е3. Дванадцять молодших розрядів адреси

вибирають комірку у субмодулі. Старші розряди адреси

декодуються для формування сигналів вибору кристала

Сигнал

дозволу роботи дешифратора Е = Е1Е2Е3. Дванадцять молодших розрядів адреси

вибирають комірку у субмодулі. Старші розряди адреси

декодуються для формування сигналів вибору кристала ![]() .

Сигналом

.

Сигналом ![]() визначається інтервал виконання операції

читання.

визначається інтервал виконання операції

читання.

Однією з умов дозволу роботи дешифратора є низький

рівень сигналу ІO/М.

Рисунок 3 –

Приклад адресації модуля пам'яті.

Приклад 4

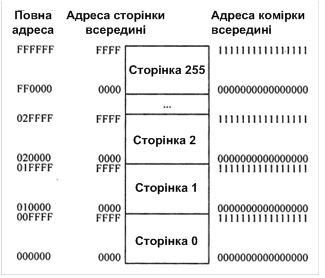

На рисунку 4 для адресації модулів пам'яті, складеного

із субмодулей з організацією 2Кх8 при розміщенні

адрес у зоні адресного простору (АП), що починається з адреси 8000Н, використовується

дешифратор. Якщо адреса знаходиться в межах 8000H...BFFFH, то робота

дешифратора дозволена, тому що цим межам

відповідають умови А15 = 1 і A14 = 0. Область АП, що

лежить у зазначених межах, у залежності від значень біт A13...A11

поділяється на частини по 2К (0800Н). Кожний з виходів дешифратора сигналом ![]() може вибирати мікросхему пам’яті з числом

збережених слів 2К. Лінії адреси А10-0 адресують комірки на

кристалі.

може вибирати мікросхему пам’яті з числом

збережених слів 2К. Лінії адреси А10-0 адресують комірки на

кристалі.

Рисунок 4 – Варіант адресації модуля пам'яті.

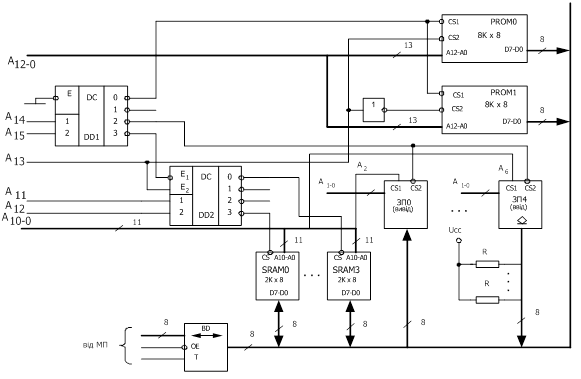

Приклад 5

Розглянемо приклад розміщення в АП модулів ПЗП, ОЗП і зовнішніх

пристроїв (ЗП). Для пам'яті використовуємо абсолютну адресацію, а для ЗП -

лінійну селекцію. Нехай для ПЗП відведено 16К адреси на початку АП, адреси ЗП

займають третю чверть АП, а адреси ОЗП займають останні 8К адресного простору.

Приймемо, що в системі мається 5 ЗП, кожний з яких має 4 внутрішніх регістри зі

своїми адресами, а як ОЗП

використовується тригерне ЗП. Розподіл

АП показаний на рисунку 5.

Рисунок 5 – Приклад розподілу адресного простору між

модулями пам'яті і зовнішніх пристроїв.

Нехай ПЗП будується на мікросхемах з організацією

8Кх8, а ОЗП на мікросхемах 2Кх8. Для адресації ЗП використовуємо молодші

розряди шини адреси, число яких визначається як N + 2, де N - число ЗП, а дві

лінії потрібні для адресації їх внутрішніх регістрів. Схема адресації, яка

відповідає таблиці адрес (таблиця 1), наведена на рисунку 6. Дешифратор DD1

розподіляє АП на чотири частини, його виходи дозволяють роботу тим об'єктам

адресації, що розташовані у відповідній чверті АП. Лінія А13 дозволяє

роботу мікросхеми PROM0 у першій половині першої чверті АП при нульовому стані

і роботу мікросхеми PROM1 - при одиничному. Лінії А2..А6 використані

для лінійної селекції зовнішніх пристроїв, а лінії A12 і А11

декодуються дешифратором DC2, для дозволу роботи мікросхемам SRAM3...SRAM0 у їх

зонах адрес

Рисунок 6 – Схема адресації модулів пам'яті і зовнішніх

пристроїв.

Рисунок 6 – Схема адресації модулів пам'яті і зовнішніх

пристроїв.

Таблиця 1 – Схема адресації

|

Об'єкт |

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

|

PROM0 |

0 |

0 |

0 |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

|

PROM1 |

0 |

0 |

1 |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

|

ЗП 0 |

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

1 |

d |

d |

|

ЗП 1 |

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

1 |

0 |

d |

d |

|

ЗП 2 |

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

1 |

0 |

0 |

d |

d |

|

ЗП 3 |

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

0 |

1 |

0 |

0 |

0 |

d |

d |

|

ЗП 4 |

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

1 |

0 |

0 |

0 |

0 |

d |

d |

|

SRAM0 |

1 |

1 |

1 |

0 |

0 |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

|

SRAM1 |

1 |

1 |

1 |

0 |

1 |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

|

SRAM2 |

1 |

1 |

1 |

1 |

0 |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

|

SRAM3 |

1 |

1 |

1 |

1 |

1 |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

d |

Символом "X" позначені байдужні стани адресних розрядів, буквою d - розряди, що входять до складу адресних входів самих

мікросхем пам'яті або адресних ліній внутрішніх регістрів ЗП.

Приклад 6

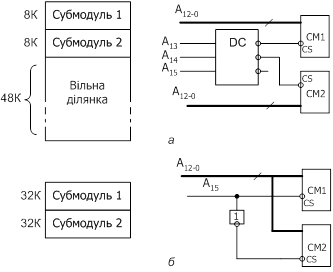

З метою спрощення схем декодування і при наявності

"зайвого" адресного простору можна застосувати неабсолютну адресацію,

при якій кожному об'єкту адресації привласнюється не одна єдина адреса, а група

адрес (деяка зона АП). Наприклад, в АП ємністю 64К потрібно розмістити всього

два субмодуля пам'яті по 8К адрес у кожному. При

абсолютній адресації (рисунок 7, а) на адресні входи самих ІС пам'яті надходять

13 молодших розрядів адреси для адресації 8К комірок субмодуля. Розряди, що залишилися, A15-13

надходять на дешифратор, нульовий і одиничний виходи якого дозволяють роботу субмодулей СМ1 і СМ2. Інші виходи дешифратора можуть бути

використані для підключення інших об'єктів адресації в зоні АП, що залишилася

вільної (48К).

При неабсолютній адресації лінії адреси A12-А0

подаються на адресні входи ІС, а для вибору однієї з них використовується лінія

А15. Лінії А14 і А13 не використовуються

взагалі, їхні стани байдужні. Схема адресації (рисунок 7, б) спрощується,

замість дешифратора "3 на 8"

потрібний тільки інвертор. Платою за це є заняття двома субмодулями

по 8К усього АП. Дійсно, всі адреси виду 0XXdd...d належать субмодулю

СМ1, а це відповідає верхнім 32К АП. Всі адреси виду 1XXdd...d належать субмодулю СМ2 і займають 32К в нижньої частини АП.

Рисунок 7 – Приклади реалізації абсолютної (а) і

неабсолютної (б) адресації субмодулей пам'яті.

Неабсолютна адресація – досить гнучкий підхід для

побудови схем декодування адреси. Для адресації об'єкта можна використовувати

більш-менш широку зону АП, вибираючи

при необхідності компроміс між крайніми рішеннями, показаними на рисунку 7.

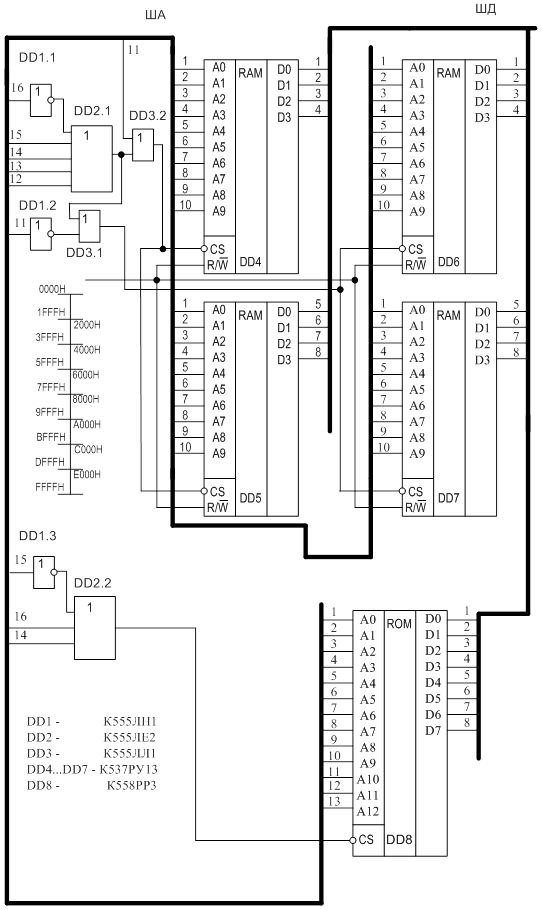

Приклад 7

Рисунок 8 – Схема

модулів пам'яті ОЗП та ПЗП мікропроцесорної системи

Для схеми:

1.

Наведіть організацію ІМС ОЗП

2.

Наведіть організацію ІМС ПЗП

3.

Визначте об’єм ОЗП МПС.

4.

Визначте об’єм ПЗП МПС.

5.

Намалюйте адресний простір МПС та покажіть

де розташовані субмодулі ОЗП та ПЗП.

6.

Визначте, який діапазон шістнадцятирічних

адрес можуть активізувати модулі ОЗП.

7.

Визначте, який діапазон шістнадцятирічних

адрес можуть активізувати модулі ПЗП.

8.

Визначте, чи можуть шістнадцятирічні

адреси 607F, 57FA, 5F00, 15D0, AFF3 активізувати модулі пам’яті, і якщо так, то які з них.

9.

Наведіть схему керування субмодулями ОЗП, якщо початковий

об’єм ОЗП збільшений у два рази.

10.

Наведіть схему керування субмодулями ПЗП, якщо початковий

об’єм ПЗП збільшений у два рази.

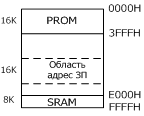

Відповідь:

1. Організація

ІМС ОЗП – 1КБіт х 4

2. Організація

ІМС ПЗП – 8КБіт х 8

3. ОЗП

МПС має об’єм 2 КБайт

4. ОЗП

МПС має об’єм 8 КБайт

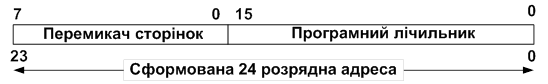

5. Адресний

простір МПС наведений на рисунку 9.

6. Для

активізації модулів ОЗП на старших розрядах шини адреси повинні бути

встановлені такі рівні сигналів 1000

0ххх хххх хххх, що

відповідає діапазону адрес: 8000h-87Ffh.

7. Для

активізації модулів ПЗП на старших розрядах шини адреси повинні бути

встановлені такі рівні сигналів 010х хххх хххх хххх,

що відповідає діапазону адрес: 4000h-5FFFh.

8. Шістнадцятирічні

адреси 57FA, 5F00

можуть активізувати модуль ПЗП.

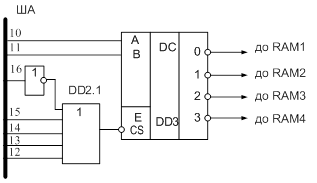

9. Якщо початковий об’єм ОЗП збільшити у два рази, то для керування

модулями потрібно застосувати дешифратор 2 на 4, схема застосування якого наведена на рисунку 10.

10. Якщо початковий об’єм ПЗП збільшити у два рази, то для керування

модулями потрібно застосувати дешифратор 2 на 4, схема застосування якого

наведена на рисунку 11 і задіяти

додатково третій адресний простір МПС

![]()

Рисунок 9 – Розподіл адресного

простору (до рисунку 8)

Рисунок 10 –

Схема керування модулями ОЗП

Рисунок 11 – Схема керування модулями ПЗП

Приклад 8

Розробити

блок пам’яті, що підключається до шин мікропроцесорної системи (шина адреси –

16розрядна, шина даних – 8 розрядна), розробити функціональну схему, навести

опис роботи:

|

Область

ОЗП |

Організація

ОЗП |

Об’єм

ОЗП |

|

4-7

(32-64КБайт) |

8Кх8 |

32КБайт |