Елементи пам'яті МПС

1 Основні

відомості. Система параметрів. Класифікація

2 Принципи

організації кеш-пам'яті

3 Запам'ятовуючі

пристрої типу ROM(M), PROM, EPROM, EEPROM

5 Статичні запам'ятовуючі пристрої

6

Побудова модулів оперативного запам’ятовувального пристрою динамічного типа

7 Динамічні запам'ятовувальні пристрої підвищеної швидкодії

1 Основні

відомості. Система параметрів. Класифікація

Запам'ятовуючі пристрої (ЗП) служать для збереження інформації й обміну нею

з іншими ЦП.

Розрізняють наступні рівні пам’яті ЕОМ:

·

регістрові ЗП, що знаходяться в складі

процесора або інших пристроїв, завдяки яким зменшується число звертань до інших

рівнів пам'яті, реалізованим поза процесором і вимагають більшого часу для

операцій обміну інформацією;

·

кеш-пам'ять, що служить для збереження

копій інформації, яка використовується в поточних операціях обміну. Висока

швидкодія кеш-пам'яті підвищує продуктивність ЕОМ;

·

основна пам'ять (оперативна, постійна,

напівпостійна), що працює в режимі безпосереднього обміну з процесором і по

можливості погоджена з ним по швидкодії.

Фрагмент програми, що виконується в поточний момент, обов'язково знаходиться в основній пам'яті;

·

спеціалізовані види пам'яті, характерні

для деяких специфічних архітектур (багатопортові, асоціативні, відеопам'ять і

ін.);

·

зовнішня пам'ять, що зберігає великі

обсяги інформації. Ця пам'ять реалізується на основі пристроїв з рухливим

носієм інформації (магнітні й оптичні диски, магнітні стрічки й ін.).

Інформаційна місткість – максимально можливий обсяг збереженої

інформації.

Організація ЗП – добуток числа збережених слів на їхню розрядність.

Це дає інформаційну місткість ЗП, однак при одній і тій же інформаційній місткості

організація ЗП може бути різною, так що організація є самостійним важливим

параметром.

Швидкодія (продуктивність) ЗП оцінюють часом читання, запису і

тривалістю циклів читання/запису. Час читання – інтервал між моментами появи

сигналу читання і слова на виході ЗП. Час

запису – інтервал після появи сигналу запису, достатній для встановлення

комірки пам’яті в стан, що задається вхідним словом. Тривалість циклів читання/запису

можуть перевищувати час читання або запису, тому що після цих операцій може знадобитися час для

відновлення необхідного початкового стану ЗП.

Для деяких режимів сучасних ЗП уводять параметр час доступу при першому

звертання (Latency) і темп передачі для наступних слів пакета

(Bandwidht). Темп передач у свою чергу оцінюється двома значеннями – граничним

(усередині пакета) і усередненим (з врахуванням Latency). Крім зазначених

основних параметрів для ЗП вказують ще цілий набір часових інтервалів.

Перераховані вище динамічні параметри є експлуатаційними (вимірюваними).

Крім них, існує ряд режимних параметрів (рівні напруг, струми, ємності

виводів, температурний діапазон і т.д.), забезпечення яких необхідно для

нормального функціонування ЗП.

2 Принципи організації кеш-пам'яті

Збільшення місткості пам'яті МПС обумовлює зниження

швидкодії операцій обміну інформацією між процесором і модулем пам'яті. Даже

за час звернення до пам'яті, рівний 70 нс, неможливо отримати необхідну інформацію

за один цикл шини. Це наводить до необхідності виконання тактів очікування в

процесі роботи процесора для того, щоб час звернення до пам'яті був погоджений

з часом виконання команди в процесорі. Підвищення швидкодії обміну інформацією

можливо за допомогою організації додаткової швидкодіючої пам'яті порівняно

невеликій місткості, звернення до якої відбувається на тактовій частоті

процесора. Така пам'ять отримала назву кеш-пам'яті, або буферної пам'яті.

Кеш-пам'ять реалізується на базі БІС ОЗП статичного типа. Інформаційна місткість

і принцип організації кеш-пам'яті визначають продуктивність роботи МПС.

Кеш-пам'ять використовують не лише для обміну

даними між МП і ОЗП, але і для обміну між ОЗП і зовнішніми накопичувачами. У

основу роботи кеш-пам'яті покладені принципи часової і просторової

локальності програм.

-

Принцип

часової локальності полягає в тому, що при читанні даних з пам'яті існує висока

ймовірність того, що впродовж деякого невеликого проміжку часу програма знову звернеться

до тих же даних.

-

Принцип

просторової локальності базується на високій ймовірності того, що програма

через деякий невеликий проміжок часу звернеться до елементу пам'яті, наступного

за тією, до якої вона зверталася перед цим.

Відповідно до принципу часової локальності інформацію

в кеш-пам'яті доцільно зберігати впродовж деякого часу, а принцип просторової

локальності вказує на доцільність розташування в кеш-пам'яті вмісту декількох

сусідніх комірок, тобто певного блоку інформації. Лінійні ділянки програм (без

переходів) в більшості випадків не перевищують 3—5 команд, тому недоцільно

використовувати блоки інформації, місткість яких перевищує місткість пам’яті,

потрібну для зберігання 3–5 команд. Як правило, інформація з основної пам'яті

завантажується в кеш-пам'ять блоками по 2–4 слова і зберігається там деякий

час.

Кеш-пам'ять запам'ятовує копії інформації, переданої між

пристроями (насамперед між процесором і основною пам'яттю). Вона має невелику місткість

у порівнянні з основною пам'яттю й більш швидкодіюча). При читанні даних

спочатку виконується звертання до кеш-пам'яті (рисунку 1). Якщо в кеш є копія

даних адресованого осередку основної пам'яті, то кеш виробляє сигнал Hit

(влучення) і видає дані на загальну шину даних. У противному випадку сигнал Hit не

виробляється й виконується читання з основної пам'яті й одночасне передаються

зчитані дані у кеш.

Рисунок 1 –

Структура кеш пам'яті

При використанні процесором кеш-пам'яті основна пам'ять

звільняється, і може виконуватись

регенерація даних у динамічному ЗП або використання пам'яті іншими

пристроями.

Залежно від способу відображення інформації з

основної пам'яті на кеш-пам'ять розрізняють типи кеш-пам'яті:

-

кеш-пам'ять з

прямим відображенням;

-

повністю

асоціативна кеш-пам'ять;

-

множинна

асоціативна кеш-пам'ять.

Кеш-пам'ять з прямим

відображенням є найбільш простим типом кеш-пам'яті (рисунок 2). Кеш-пам'ять

містить дві частини – кеш-пам'ять даних і кеш-пам'ять ознак. Передбачимо, що місткість

ОЗП МПС дорівнює 4 Гбайт. Ця місткість розбивається на 64 К рівних частин по 64

Кбайт. Блок даних ємкістю 4 байт пересилається з кожної частини ОЗП в один

32-розрядний рядок кеш-пам'яті даних. Місткість кеш-пам'яті даних складає 64

Кбайт, тому кількість рядків дорівнює 64 Кбайт/ 4 байт = 16 К. Таким образом,

під будь-яку з 64К частин ОЗП в кеш-пам'яті відводиться один рядок: 32-розрядна

адреса 4-байтного блоку в ОЗП ділиться на дві частини. Молодші 16 розрядів

адреси А15–А0 називають індексом, старші 16 розрядів А31—А16 — ознакою. Ознака

пересилається в кеш-пам'ять ознак, яка містить 16 К рядків і має загальну місткість

32 Кбайт.

Рисунок 2 – Структурна схема кеш-пам'яті з прямим

відображенням

Для визначення адреси одного рядка кеш-пам'яті

даних необхідно 14 адресних розрядів А15–А2, а для визначення одного байта в

рядку – 2 розряди А1, А0.

При необхідності читання даних з пам'яті процесор

звертається спочатку до кеш-пам'яті і перевіряє, чи містить вона потрібні дані.

Цей процес відбувається шляхом порівняння ознаки, записаної в кеш-пам'яті

ознак, з 16 старшими розрядами адреси, яку процесор виставляє на 32-розрядну

шину адреси. Збіг цих величин означає, що в кеш-пам'яті зберігаються необхідні

дані, які потім і читаються з кеш-пам'яті. Якщо величини не збігаються, то

виконується копіювання відповідних даних з оперативної пам'яті в кеш-пам'ять.

Перевагою такого типа кеш-пам'яті є порівняно

висока швидкодія, що пояснюється необхідністю виконання лише одного порівняння

ознаки із старшими розрядами адреси ОЗП.

Недоліком кеш-пам'яті з прямим відображенням є

виникнення конфліктів в разі, якщо старші 16 розрядів адреси елементу пам'яті

співпадають з ознакою, записаною в кеш-пам'яті ознак, а індекси необхідного

блоку і рядка в кеш-пам'яті даних не збігаються. Це означає, що рядок в кеш-пам'яті

даних, відведена для цієї частини ОЗП і визначається старшими 16 адресними

розрядами, вже зайнята. В такому разі зміст рядку кеш-пам'яті даних

пересилається назад в ОЗП, а в рядок пересилається новий необхідний 4-байтовий

блок.У результаті збільшується кількість пересилок між кеш-пам'яттю і ОЗП і час

обміну інформацією.

Структурна

схема повністю асоціативної

кеш-пам'яті показана на рисунку 3. У цій схемі усунений недолік

кеш-пам'яті з прямим відображенням, оскільки будь-який блок ОЗП може відображуватися

в будь-якому рядку кеш-пам'яті. У кеш-пам'ять ознак записується 30-розрядна

ознака, тобто старші 30 розрядів А31—А2 адреси 4-байтного блоку ОЗП. У рядок

кеш-пам'яті даних записується 4-байтный блок. Якщо кеш-пам'ять не заповнена,

блок записується в будь-який вільний рядок. Якщо кеш-пам'ять заповнена, блок з

ОЗП записується в той рядок кеш-пам'яті даних, до якої була найменша кількість

звернень. Недоліки кеш-пам'яті з прямим відображенням усуваються за рахунок

додаткових засобів визначення блоку, до якого була найменша кількість звернень.

При цьому також збільшується час обробки запитів із-за необхідності порівняння

30-розрядної адреси і ознаки, записаної в кеш-пам'яті ознак. Максимальна

кількість таких порівнянь складає 16К.

Рисунок 3 – Структурна схема повністю асоціативній

кеш-пам'яті

Множинна асоціативна

кеш-пам'ять об'єднує переваги обох попередніх типів. Рядки цієї кеш-пам'яті

об'єднуються в групи по 2, 4 і більш (відповідно до цього розрізняють

2-входовую, 4-входовую і подібну множинну асоціативну кеш-пам'ять). Структурна

схема 2-входовой множинної асоціативної кеш-пам'яті показана на рисунку 4.

Рисунок 4 – Структурна схема 2-входовой

множинної асоціативної кеш-пам'яті

Кеш-пам'ять даних складається з 8К груп, кожна з

яких містить два рядки. Індекс, тобто 16 молодших розрядів адреси ОЗП, адресує

байт в кеш-пам'яті даних (13 розрядів адресують одну з 8 К груп, 1 розряд –

рядок в групі і 2 розряди — байт в рядку). Ознака, тобто 16 старших адресних

розрядів, записується в рядок пам'яті ознак. Таким чином, для блоків з одним і

тим же індексом відводяться два рядки кеш-пам'яті. Відповідно, якщо один з

рядків групи зайнятий деяким блоком, то наступний блок з таким же індексом буде

розміщений у вільному рядку. Усередині групи кеш-пам'ять є повністю

асоціативною. Кількість порівнянь адрес ОЗП з ознаками дорівнює двом.

Зростання місткості кеш-пам'яті, тобто кількості

рядків в групі збільшує ефективність її роботи, проте при цьому зростає кількість

порівнянь адрес і, отже, час обробки запиту комірки ОЗП. Ефективність роботи

кеш-пам'яті характеризується коефіцієнтом вдалих звернень.

Всі розглянуті типи кеш-пам'яті мають властивість

зберігати окремі копії інформації, яка міститься в основній пам'яті. Під час

записи в кеш-пам'ять може порушуватися цілісність даних, що зберігаються,

тобто вміст кеш-пам'яті перестане відповідати вмісту ОЗП. Існує декілька

способів відновлення інформації в ОЗП, основними з яких є спосіб крізного

запису і спосіб зворотного запису.

Спосіб крізного запису полягає в тому, що

інформація записується як в кеш-пам'ять, так і в ОЗП.

Спосіб

зворотного запису передбачає запис інформації в ОЗП лише в тому випадку, якщо

вона змінюється в кеш-пам'яті. Кожному рядку кеш-пам'яті ставиться у

відповідність спеціальний біт – біт запису, щовказує на зміну вмісту рядка. При

заміщенні рядка кеш-пам'яті новим блоком інформації з ОЗП перевіряється стан

біта запису, і якщо цей біт встановлений, то виконується перезапис блока з

кеш-пам'яті в ОЗП. Лише після цього в кеш-пам'яті розміщується новий блок з

ОЗП. Цей спосіб ефективніший, оскільки дозволяє зменшити кількість звернень до

ОЗП.

3 Запам'ятовуючі

пристрої типу ROM(M), PROM, EPROM, EEPROM

Масочні запам'ятовуючі

пристрої

Елементом зв'язку в масочних ЗП можуть бути діоди, біполярні транзистори,

МОН –транзистори і т.д.

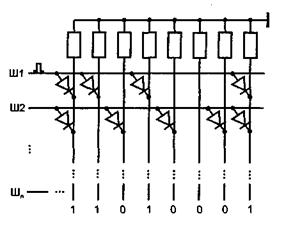

У матриці діодного ROM (рисунок 5) горизонтальні лінії є лініями вибірки

слів, а вертикальні - лініями зчитування. Слово, що зчитується визначається

розташуванням діодів у вузлах координатної сітки. При наявності діода високий

потенціал обраної горизонтальної лінії передається на відповідну вертикальну

лінію, і в даному розряді слова з'являється сигнал логічної одиниці. При

відсутності діода потенціал близький до нульового, тому що вертикальна лінія через резистор зв'язана з

землею. У зображеній матриці при звертанні до лінії вибірки Ш1 зчитується слово

11010001 (в комірці номер один зберігається це слово). При звертанні до Ш2 зчитується слово 10101011

(воно зберігається в комірці номер 2). Шини вибірки є виходами дешифратора

адреси, кожна адресна комбінація збуджує свій вихід дешифратора, що приводить

до зчитування слова з адресуємої комірки.

У матриці з діодними елементами в одних вузлах матриці діоди

виготовляються, в інших - ні. Для матриць з МОН – транзисторами часто в МОН –

транзисторах, що відповідають збереженню нуля, збільшують товщину підзатворного

окисла, що веде до збільшення граничної напруги транзистора. У цьому випадку

робочі напруги ЗП не в змозі відкрити транзистор. Постійно закритий стан

транзистора аналогічно його відсутності. Матриця з МОН – транзисторами показана

на рисунку 6.

Рисунок 5 –

Матриця діодних запам'ятовуючих елементів масочного ЗП

Рисунок 6 – Матриця МОН – транзисторних елементів.

Масочні ЗП використовують у якості "прошивки" коди букв алфавітів

(російської і латинського), таблиці типових функцій (синуса, квадратичної

функції й ін.), стандартне програмне забезпечення.

Запам'ятовуючі

пристрої типу PROM

У ЗП типу PROM мікросхеми програмуються усуненням або створенням

спеціальних перемичок. У вихідній заготівці маються (або відсутні) усі

перемички. Після програмування залишаються або виникають тільки необхідні.

Усунення частини перемичок властиво ЗП з плавкими перемичками (типу fuse -

запобіжник). При цьому у вихідному стані ЗП має всі перемички, а при

програмуванні частина їхній ліквідується шляхом розплавлювання імпульсами

струму досить великої амплітуди і тривалості.

У ЗП з плавкими перемичками ці перемички включаються в електроди діодів або

транзисторів. Перемички можуть бути металевими (спочатку виготовлялися з

ніхрому, пізніше тітановольфрамові і інших сплавів) або полікристалічними

(кремнієвими). У вихідному стані запам'ятовуючий елемент зберігає логічну

одиницю, логічний нуль потрібно записати, розплавляючи перемичку.

Створення частини перемичок відповідає схемам, які у вихідному стані мають

непровідні перемички у виді пари зустрічно включених діодів або тонких

діелектричних шарів, які пробиваються при програмуванні з утворенням низькоомних

опорів. Схеми з тонкими діелектричними

перемичками, що пробиваються, (типу antіfuse) найбільш компактні і досконалі.

Другий тип запам'ятовуючого елемента PROM - два зустрічно включених діоди.

У вихідному стані опір такого ланцюжка настільки великий, що практично

рівноцінно розімкнутому колу, і запам'ятовуючий елемент зберігає логічний нуль.

Для запису одиниці до діодів прикладають підвищена напруга, яка пробиває діод,

зміщений у зворотному напрямку. Діод пробивається з утворенням у ньому

короткого замикання і відіграє роль

провідної перемички, що з'явилася.

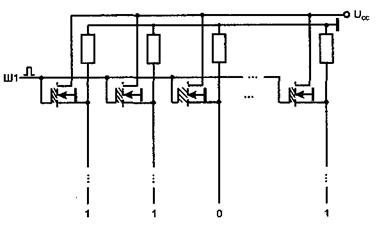

Запам'ятовуючі елементи з плавкими перемичками і парами діодів показані на рисунку

7, а, б у вихідному стані і після

програмування.

Рисунок 7 – Запам'ятовуючі елементи з

плавкими перемичками (а) і діодними парами (б).

Матриця запам'ятовуючих елементів ЗП з плавкими перемичками (мікросхеми

К155РЕЗ) показана на рисунок 8. ЗП має організацію 32x8. Матриця містить 32

транзистора з 9 емітерами. Високий потенціал на якій-небудь шині вибірки

активізує відповідний транзистор, який працює в режимі емітерного повторювача.

До програмування транзистори передають високий потенціал бази на усі вихідні

(розрядні) лінії, тобто по всім адресам

записані слова, які складаються з одних одиниць. Перепалювання перемички в колі

якого-небудь емітера дає нуль у даному розряді слова, наприклад, для комірки з

номером 1 показаний варіант програмування для збереження по цій адресі слова

10100101. Виходи матриці зв'язані з зовнішніми ланцюгами через буферні каскади,

які мають виходи типу загальний колектор (ЗК) або загальний стік (ЗС). ЗП має

структуру 2D.

Рисунок 8 – Матриця запам'ятовуючих елементів із плавкими

перемичками

Запам'ятовуючі

пристрої типу EPROM і EЕРRОМ

У репрограмуємих ЗП типів EPROM і EEPROM (або E2PROM) можливе

стирання старої інформації і заміна її нової в результаті спеціального процесу,

для проведення якого ЗП виводиться з робочого режиму. Робочий режим (читання

даних) - процес, виконуваний з відносно високою швидкістю. Заміна ж умісту

пам'яті вимагає виконання набагато більш тривалих операцій.

По способу стирання старої інформації розрізняють ЗП зі стиранням

ультрафіолетовими променями (EPROM) і електричним стиранням (E2PROM

).

Запам'ятовуючими елементами сучасних РПЗП є транзистори типів МНОН і ЛІЗМОН

(додавання ЛІЗ до позначення МОН походить від слів Лавинна Інжекція Заряду).

Імпульсне

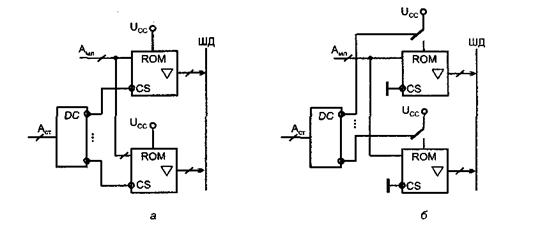

живлення ROM

Енергонезалежність усіх ROM, які зберігають інформацію при відключенні

живлення, відкриває можливості економії живлення при їхній експлуатації і

відповідно, поліпшення їхнього теплового режиму, що підвищує надійність схем.

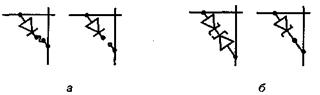

Живлення можна подавати тільки на ІС, до якої в даний момент відбувається

звертання. На рисунку 9 показаний звичайний варіант побудови модуля пам'яті,

який складається з декількох ІС, і варіант з імпульсним живлення. У звичайному

варіанті напруга Ucc підключається до всіх ІС постійно, а вибір мікросхеми, що

адресується здійснюється сигналом CS. У варіанті з імпульсним живлення робота

всіх ІС по входах CS постійно дозволена, але живлення підключається тільки до

обраної мікросхеми за допомогою ключа, керованого від виходів адресного

дешифратора, що декодують старші розряди адреси.

Режим імпульсного живлення може багаторазово зменшити споживану модулем

потужність, але, одночасно, збільшує час звертання до ЗП при одиночних

довільних звертаннях, тому що після

включення живлення необхідний час для встановлення режиму мікросхеми.

При читанні даних, розташованих по близьких адресах, коли старші розряди

адреси залишаються незмінними, втрат часу не виникає.

Рисунок 9 – Модулі постійної пам'яті

зі звичайним (а) і імпульсним (б) живленням

4 Флеш-пам’ять

Флеш-пам’ять (Flash-Memory) за типом запам'ятовуючих

елементів і основних принципів роботи подібна пам'яті типу E2PROM,

однак ряд архітектурних і структурних особливостей дозволяють виділити її в

окремий клас. У схемах Флеш-пам’яті не передбачене стирання окремих слів,

стирання інформації здійснюється або для всієї пам'яті одночасно, або для

досить великих блоків. Це дозволяє спростити схеми ЗП, тобто сприяє досягненню

високого рівня інтеграції й швидкодії при зниженні вартості.

Одночасне стирання всієї інформації ЗП реалізується

найбільше просто, але має той недолік, що навіть заміна одного слова в ЗП

вимагає стирання й нового запису для всього ЗП в цілому. Для багатьох

застосувань це незручно. Тому поряд зі схемами з одночасним стиранням усього

вмісту є схеми із блоковою структурою, у яких весь масив пам'яті ділиться на

блоки, яки стираються незалежно один від одного. Обсяг таких блоків сильно відрізняється:

від 256 байт до 128 Кбайт.

Двома основними напрямками ефективного

використання Флеш-пам’яті є зберігання даних, що не дуже часто змінюються і

заміна пам'яті на магнітних дисках.

Стирання в пристроях першого типу може бути як одночасним

для всієї пам'яті, так і блоковим. Серед пристроїв із блоковим стиранням

виділяють схеми зі спеціалізованими блоками (несиметричні блокові структури).

По імені так званих Boot-блоків, у яких інформація надійно захищена апаратними

засобами від випадкового стирання, ці ЗП називають Boof Block Flash Memory. Boot-блоки

зберігають програми ініціалізації системи, які дозволяють увести її в робочий

стан після включення живлення.

Мікросхеми для заміни жорстких магнітних дисків (Flash-File

Memory) містять більш розвинені засоби перезапису інформації й мають

ідентичні блоки (симетричні блокові структури).

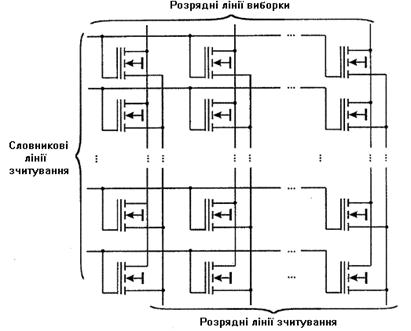

Рисунок 10 – Структура

матриці накопичувача Флеш-пам’яті

на основі елементів АБО – НІ

Одним з елементів структури Флеш-пам’яті є накопичувач (матриця

запам'ятовувальних елементів). У схемотехніці накопичувачів розвиваються два

напрямки: на основі елементів типу АБО-НІ (NOR) і на основі елементів типу І-НІ

(NAND).

Структура матриці накопичувача показана на рисунку 10.

Кожний стовпчик представляє собою сукупність паралельно з'єднаних транзисторів.

Розрядні лінії вибірки перебувають під високим потенціалом. Всі транзистори

невибраних рядків замкнені. В обраному рядку відкриваються й передають високий

рівень напруги на розрядні лінії зчитування ті транзистори, у плаваючих

затворах яких відсутній заряд електронів, і, отже, гранична напруга транзистора

має нормальне (не підвищене) значення.

Флеш-пам’ять із

несиметричною блоковою структурою

Схемам типу Boot Block Ftash Memory (ББФП) властиве

блокове стирання даних і несиметрична блокова архітектура. Блоки спеціалізовані

й мають різні розміри. Серед них є так званий Boot-блок (ББ), уміст якого

апаратно захищений від випадкового стирання. У ББ зберігається програмне забезпечення

базової системи вводу/виводу мікропроцесорної системи BIOS (Basic Input/Output

System), необхідне для правильної експлуатації й ініціалізації системи.

У складі блоків є також БП (блоки параметрів) і ГБ

(головні блоки), не забезпечений апаратними засобами захисту від

непередбачуваного запису. Блоки БП зберігають відносно часто змінювані

параметри системи (коди ідентифікаторів, діагностичні програми й т.п.). Блоки

ГБ зберігають основні керуючі програми й т.п.

Мікросхеми ББФП призначені для роботи з різними

мікропроцесорами й для відповідності їм мають два варіанти розташування ББ в

адресному просторі: угорі й унизу, що відображається в маркуванні МІКРОСХЕМА

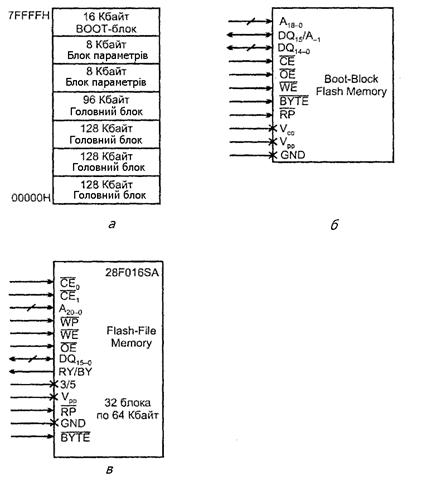

буквами Т (Тор) або В (Bottom). На рисунку 11, а для прикладу наведена

карта пам'яті (розподіл адресного простору) для мікросхеми ємнмікросхематю 4

Мбіт з верхнім розташуванням ББ.

За функціонуванням ББФП близькі до пам'яті типу Bulk

Erase, в обох типах мікросхем операції стирання/програмування ведуться під

керуванням внутрішнього автомата, вхідною інформацією для якого служать

команди, що надходять від процесора. У схемах ББФП цю роль грає командний

інтерфейс користувача CUI (Command User Interface).

Зовнішня організація типової ББФП зображена на рисунку 11,

б на прикладі мікросхеми із інформаційною ємністю 4 Мбіта.

Адреси задаються 19-розрядним кодом А18–0,

тобто в пам'яті зберігається до 512 Кслов. Сигнал ![]() задає 8-розрядну або

16-розрядну організацію пам'яті. При байтовій організації байти передаються по

лініях DQ7-0, a лінія DQ15 відіграє роль самого молодшого

розряду адреси А-1, що визначає, який байт даної комірки передається

(старший або молодший). При словниковій організації виводи DQ15-0 є

лініями вводу-виводу даних.

задає 8-розрядну або

16-розрядну організацію пам'яті. При байтовій організації байти передаються по

лініях DQ7-0, a лінія DQ15 відіграє роль самого молодшого

розряду адреси А-1, що визначає, який байт даної комірки передається

(старший або молодший). При словниковій організації виводи DQ15-0 є

лініями вводу-виводу даних.

Напруга на виводі ![]() (Reset/Power Down)

може мати три рівні: 12В, рівень логічної одиниці Н и низький рівень L. При

напрузі 12В ББ відкритий і в ньому можуть виконуватися операції стирання й

програмування. При напрузі нижче 6,5В ББ зачинений.

(Reset/Power Down)

може мати три рівні: 12В, рівень логічної одиниці Н и низький рівень L. При

напрузі 12В ББ відкритий і в ньому можуть виконуватися операції стирання й

програмування. При напрузі нижче 6,5В ББ зачинений.

Рисунок 11 – Розподіл

адресного простору й зовнішня організація Флеш-пам’яті з несиметричною блоковою

структурою (а, б) і зовнішня організація файлової Флеш-пам’яті (в).

Маючи ряд режимів економії потужності, схеми ББФП,

зокрема, реалізують режим APS (Automatic Power Saving), завдяки якому після

завершення циклу читання схема автоматично входить у статичний режим зі

споживанням струму близько 1 мА, у якому перебуває до початку наступного циклу

читання.

Коли схема не обрана (при високому рівні сигналу на

виводі ![]() й виводі

й виводі ![]() , тобто

, тобто ![]() =

= ![]() = Н) споживання потужності знижується до рівня спокою

(десятки мкА). При

= Н) споживання потужності знижується до рівня спокою

(десятки мкА). При ![]() = L не тільки

забороняється запис, але й уводиться режим глибокого зниження потужності, у

якому струм споживання знижується до часток мкА.

= L не тільки

забороняється запис, але й уводиться режим глибокого зниження потужності, у

якому струм споживання знижується до часток мкА.

Активному режиму відповідає комбінація сигналів ![]() = L і

= L і ![]() = Н. Сигнали

= Н. Сигнали ![]() й

й ![]() мають звичайне

призначення. Мікросхеми Boot-блок Флеш-пам’яті можуть працювати з різними

напругами живлення й програмування (технологія Smart Voltage), мають час

доступу при читанні 60...70 нс, струми активних режимів 15...25 мА й украй малі

струми в режимі глибокого зниження потужності (близько 0,2 мкА).

мають звичайне

призначення. Мікросхеми Boot-блок Флеш-пам’яті можуть працювати з різними

напругами живлення й програмування (технологія Smart Voltage), мають час

доступу при читанні 60...70 нс, струми активних режимів 15...25 мА й украй малі

струми в режимі глибокого зниження потужності (близько 0,2 мкА).

Файлова

Флеш-пам’ять

Важливе місце

в ієрархії ЗП займає файлова Флеш-пам’ять

(ФФП). Накопичувач ФФП ділиться на блоки, які служать аналогами секторів

магнітних дисків, як в операційній системі MS-DOS. Розроблені програмні засоби,

які забезпечують обмін між Флеш-блоками, подібно тому як операційна система

MS-DOS забезпечує обмін між секторами диска.

Блоки ФФП ідентичні й мають однакову інформаційну місткість

(симетрична блокова архітектура). Тому що у ФФП операції запису виконуються

значно частіше, ніж в інших різновидах Флеш-пам’яті, цим операціям приділяється

велика увага - уводяться сторінкові буфери, що дозволяють із високою швидкістю

накопичувати деякий обсяг даних, підлягаючих запису, для їхньої наступної

передачі в накопичувач із меншою швидкістю.

Зовнішня організація ФФП показана на рис. 13, в, на

прикладі мікросхеми з інформаційною ємністю 16 Мбіт (ІС типу 28FQ16SA фірми

Intel).

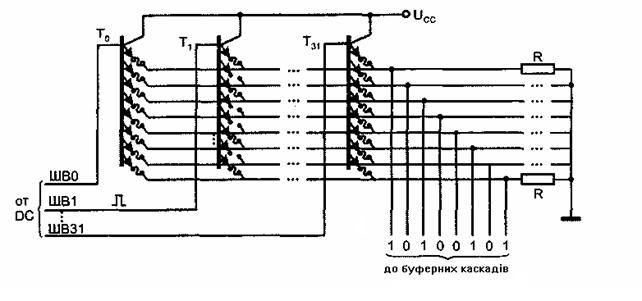

Накопичувач схеми із загальною інформаційною ємністю 16

Мбіт розбитий на 32 блоки по 64 Кбайт.

Шина адреси: лінії А20-16 вибирають один із

блоків, лінії A15-1 вибирають слово в межах одного блоку (блок з

ємністю 64 Кбайта містить 32 Кслов), лінія А0

– біт вибірки байта, що визначає старший і молодший байти при байтовій організації

пам'яті й відключається при її словниковій організації. Від процесора надходить

початкова адреса блоку даних, яка запам'ятовується в черзі адрес. Поточна

адреса комірки пам'яті для обміну формується адресним лічильником.

У шині даних DQ15-0 лінії DQ7-0

призначені для вводу й виводу молодшого байта даних, передачі команди в

командний інтерфейс користувача CUI у циклі запису й виводу даних з буфера,

регістрів ідентифікатора або стану у відповідних режимах читання. Лінії DQ15-8

призначені для передачі старшого байта при словниковій організації

пам'яті. По них виводять дані накопичувача, буфера або ідентифікатора у

відповідному режимі читання, але ці лінії не використаються для читання з

регістрів стану. Якщо кристал не обраний або заборонений вивід лінії шини даних

переходять у третій стан.

Лінії ![]() 0 й

0 й ![]() І — входи дозволу кристала, при високому рівні

кожного з них кристал не обраний, і споживання потужності знижується до рівня

стану спокою (Standby) після завершення поточної операції запису або стирання.

І — входи дозволу кристала, при високому рівні

кожного з них кристал не обраний, і споживання потужності знижується до рівня

стану спокою (Standby) після завершення поточної операції запису або стирання.

Сигнал ![]() відкриває вихідні

буфери при низькому рівні й переводить їх у третій стан при високому рівні.

відкриває вихідні

буфери при низькому рівні й переводить їх у третій стан при високому рівні.

Сигнал ![]() керує доступом до

командного інтерфейсу користувача CUI, сторінковим буферам, регістрам черги

даних і засувкам черги адрес.

керує доступом до

командного інтерфейсу користувача CUI, сторінковим буферам, регістрам черги

даних і засувкам черги адрес.

Сигнал ![]() (Reset/Power-Down) при

низькому рівні вводить схему в стан глибокої економії потужності, відключаючи

всі схеми, що споживають статичну потужність. При виході із цього стану час

відновлення схеми становить 400 нс. При переході до низького рівня операції

автомата записи припиняються, схема скидається.

(Reset/Power-Down) при

низькому рівні вводить схему в стан глибокої економії потужності, відключаючи

всі схеми, що споживають статичну потужність. При виході із цього стану час

відновлення схеми становить 400 нс. При переході до низького рівня операції

автомата записи припиняються, схема скидається.

Сигнал RY/BY (Ready/Busy) показує стан внутрішнього

автомата запису. Низький рівень означає зайнятість, високий означає або

готовність до нових операцій, або призупинення стирання, або стан глибокої

економії потужності залежно від виконуваної операції.

Сигнал ![]() (Write Protect) має

наступний сенс. Кожний блок має біт заборони запису (Lock-bit). Низький рівень

(Write Protect) має

наступний сенс. Кожний блок має біт заборони запису (Lock-bit). Низький рівень ![]() дозволяє захист, тобто запис або стирання в блоці можуть

виконуватися тільки при Lock-bit = 0. При високому рівні

дозволяє захист, тобто запис або стирання в блоці можуть

виконуватися тільки при Lock-bit = 0. При високому рівні ![]() у блоках можуть виконуватися операції запису й стирання

незалежно від стану блокуючих біт.

у блоках можуть виконуватися операції запису й стирання

незалежно від стану блокуючих біт.

Сигнал ![]() низьким рівнем уводить схему в байтовий режим, високим — у

словниковий і виключає буфер лінії a0.

низьким рівнем уводить схему в байтовий режим, високим — у

словниковий і виключає буфер лінії a0.

Напруга програмування UРР і вивід напруги

живлення (це може бути 3,3 або 5В — вхід позначений дробом 3/5) надходять у схему

через перемикач напруги, що перебуває усередині схеми.

Пам'ять типу

StrataFlash

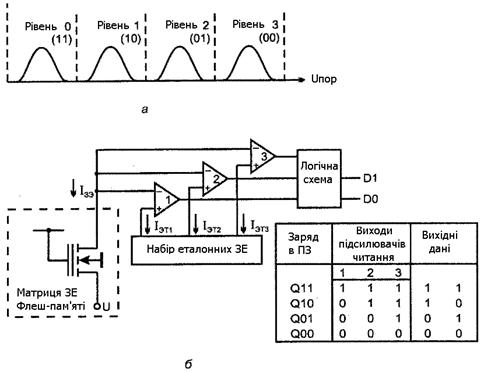

В 1997 р. компанія Intel представила новий вид

Флеш-пам’яті, названий StrataFfash, у якій уперше в одному елементі пам'яті

зберігаються два біти, а не один. Це забезпечується тим, що в плаваючому

затворі транзистора фіксується не тільки наявність або відсутність заряду, але

й визначається його величина, яка може мати кілька значень. Розрізняючи чотири

рівні, можна зберігати в одному елементі два біти.

До винаходу пам'яті СтратаФлеш для збільшення ємності ЗП

йшли шляхом зменшення розмірів схемних елементів і інших удосконалень

технологічних процесів літографії. СтратаФлеш ознаменувала інший підхід до цієї

проблеми. Зберігання двох біт домоглися практично в тих же запам'ятовуючих

елементах, які раніше зберігали один біт, переборовши труднощі жорсткості

допусків на величини зарядів, які вводять у плаваючий затвор. У другій половині

90-х рр. з'явилися комерційні зразки пам'яті СтратаФлеш. При цьому від ємності 32 Мбіта перейшли до ємності 64 Мбіта без

помітних змін площі кристала.

Рисунок 12 – Графіки

розподілу граничних напруг у чотирьохрівневому запам'ятовуючому елементі (а)

і схема читання даних із цього елемента (б)

Запам'ятовуючі елементи програмуються введенням у плаваючий

затвор одного з 4-х кількостей заряду, кожне з яких відповідає парі двійкових

цифр 11, 10, 01, 00. Залежно від заряду, який запам'ятовує транзистор має один

із чотирьох граничних напруг. При зчитуванні інформації до затвора транзистора

прикладають напругу зчитування. Струм запам'ятовуючого транзистора залежить від

граничної напруги. Визначаючи струм, можна виявити стан плаваючого затвора. На

рис. 12 показані розподіл граничних напруг у чотирьохрівневому запам'ятовуючому

елементі (а) і схема читання стану запам'ятовуючого транзистора (б).

5 Статичні запам'ятовуючі пристрої

Статичні ОЗП енергозалежні - при знятті живлення інформація в тригерних

запам'ятовуючих елементах губиться. Можна додати їм штучну енергозалежність за

допомогою резервного джерела живлення. Це найбільш придатне для ЗП на елементах

КМОН, тому що вони в режимі зберігання

споживають надзвичайно малу потужність.

Для підключення до накопичувача ЗП резервного джерела живлення розроблювачі

пам'яті рекомендують схему, приведену на рисунок 13. У цій схемі напруга

резервного джерела трохи нижче напруги основного джерела Ucc. У робочому режимі

накопичувач живиться від напруги Ucc, при цьому діод Д1 проводить, а діод Д2

замкнений. При зниженні робочої напруги до накопичувач автоматично підключається

джерело резервного живлення. При цьому проводить діод Д2, а діод Д1

закривається, тому що при малих

значеннях Ucc він попадає під зворотний зсув.

При розробці мікропроцесорних систем варіант (рисунок 13, а) недостатньо

надійний у зв'язку з наступною обставиною. Напруга живлення системи Ucc

виробляється джерелом, на виході якого звичайно мається фільтр, який згладжує зі значною інерційністю. Тому при аварії

живлення напруга Ucc не зникає відразу, а відносно повільно знижується. На

початковому етапі цього процесу система продовжує працювати, але в її роботі

можливі помилки. Бажано швидше відреагувати на аварію живлення. Це досягається

за допомогою схеми (рисунок 13, б).

Рисунок 13 – Схеми підключення резервних джерел живлення

Порушення нормальної роботи джерела живлення виявляється контролем напруги

змінного струму (АС - Alternate Current).

Порушення можна виявити за один-два періоди змінної напруги, поки постійна

напруга Ucc ще не змінилося. Ознака порушення AC_low служить запитом

переривання для процесора CPU. Одержавши запит, процесор виконує підпрограму

обслуговування переривання A (Interrupt А), у ході

якого передає уміст своїх регістрів у стек накопичувача (виконує контекстне

переключення) і закінчує підпрограму установкою тригера Т, який впливає на

обмотку реле, яка керує ключем. У результаті пам'ять підключається до

резервного джерела.

6 Побудова модулів оперативного

запам’ятовувального пристрою динамічного типа

У мікросхемах ОЗП динамічного типа елементом

пам'яті є місткість p-n-переходу МДП-транзистора. Заряджений стан конденсатора

вважається станом логічної одиниці, розряджений – станом логічного нуля. Такі

елементи пам'яті не можуть тривалий час зберігати свій стан і тому вимагають

додаткових засобів для забезпечення періодичного відновлення (регенерації)

інформації. Час вибірки для динамічного ОЗП складає 70— 200 нc. У порівнянні з

ОЗП статичного типу ОЗП динамічного типа характеризуються: більшою

інформаційною ємкістю, обумовленою меншим числом компонентів в одному елементі

пам'яті; меншою швидкодією (із-за необхідності заряду і розряду конденсатора

при записі біта інформації); меншою потужністю споживання; меншою вартістю.

У більшості випадків модулі оперативної пам'яті

сучасних МПС реалізуються на базі БІС ОЗП динамічного типа.

Для забезпечення адресації порівняно великої місткості

динамічної пам'яті використовують мультиплексування адресних сигналів в часі.

Спочатку на БІС ОЗП подають m

молодших розрядів шини адреси, що супроводжуються стробом ![]() (Row Address

Strobe, строб адреси рядка). Потім m – старших, супроводжуються стробом

(Row Address

Strobe, строб адреси рядка). Потім m – старших, супроводжуються стробом ![]() (Column

Address Strobe, строб адреси стовпця). Мультиплексування адресних ліній в часі

дозволяє зменшити число виводів БІС ОЗП для адреси в 2 рази. Так для БІС

К5656РУ7 за допомогою восьми адресних ліній А7–А0 передаються дані, адресація

яких вимагає 16 адресних ліній. Ця БІС

має інформаційну місткість 64К х 1 і два виводи, на яких поступають сигнали

стробів

(Column

Address Strobe, строб адреси стовпця). Мультиплексування адресних ліній в часі

дозволяє зменшити число виводів БІС ОЗП для адреси в 2 рази. Так для БІС

К5656РУ7 за допомогою восьми адресних ліній А7–А0 передаються дані, адресація

яких вимагає 16 адресних ліній. Ця БІС

має інформаційну місткість 64К х 1 і два виводи, на яких поступають сигнали

стробів ![]() і

і ![]() .

.

ОЗП динамічного типа працюють в таких режимах:

запис, читання, читання – модифікація - запис, сторінковий запису, сторінкового

читання, регенерації. Читання інформації здійснюється по задньому фронту

сигналу ![]() при

при ![]() = 1, запис – по задньому фронту сигналу

= 1, запис – по задньому фронту сигналу ![]() при

при ![]() = 1. Режим

читання – модифікація – запис полягає в читанні інформації з подальшим записом

в той же елемент пам'яті. Сторінкові режими запису і читання реалізуються зверненням

до мікросхеми за адресою рядка з вибіркою різних елементів пам'яті цього рядка

при зміні адрес стовпців. Регенерація інформації здійснюється зверненням до

кожного з рядків, при цьому формується адреса рядка і сигнал

= 1. Режим

читання – модифікація – запис полягає в читанні інформації з подальшим записом

в той же елемент пам'яті. Сторінкові режими запису і читання реалізуються зверненням

до мікросхеми за адресою рядка з вибіркою різних елементів пам'яті цього рядка

при зміні адрес стовпців. Регенерація інформації здійснюється зверненням до

кожного з рядків, при цьому формується адреса рядка і сигнал ![]() , а сигнал

, а сигнал ![]() має рівень логічної одиниці. Процес регенерації

припиняється при зверненні МП до ОЗП. В цьому випадку обробляється запит МП,

після чого процес регенерації продовжується з тієї адреси, на якій він був

припинений.

має рівень логічної одиниці. Процес регенерації

припиняється при зверненні МП до ОЗП. В цьому випадку обробляється запит МП,

після чого процес регенерації продовжується з тієї адреси, на якій він був

припинений.

Рисунок 14 –

Структурна схема контролера динамічної пам'яті i8207

Для управління ОЗП динамічного типа використовують

контролери динамічної пам'яті, наприклад, К1810ВТ03, К1810ВТ02, i8207.

Контролер динамічної пам'яті i8207 (рис. 14) призначений для управління

чотирма БІС ОЗП динамічного типа ємкістю 512 Кбайт кожна. Він складається з

адресних буферів B1 і В2, лічильника рядків регенерації (РСР), мультиплексорів

M1 і М2 і системи управління. Система управління аналізує вхідні сигнали і

здійснює управління всіма блоками контролера. При виконанні команд

читання/запис пам'яті контролер забезпечує з'єднання виходів АО8—АО0 спочатку з

молодшою, а потім із старшою половинами адреси, формування строб сигналів ![]() і

і ![]() для кожної

з чотирьох БІС пам'яті, а також сигналу

для кожної

з чотирьох БІС пам'яті, а також сигналу ![]() (Write

Enable, дозвіл запису). У режимі регенерації контролер забезпечує з’эднання з

виводами А08—АО0 виходів лічильника рядків регенерації і формування сигналу

(Write

Enable, дозвіл запису). У режимі регенерації контролер забезпечує з’эднання з

виводами А08—АО0 виходів лічильника рядків регенерації і формування сигналу ![]() . Вибір однієї з чотирьох БІС пам'яті здійснюється

сигналами BS1—BS0 відповідно таблиці 1.

. Вибір однієї з чотирьох БІС пам'яті здійснюється

сигналами BS1—BS0 відповідно таблиці 1.

Таблиця 1 – Вибір БІС

динамічній пам'яті

|

BS1 |

BS0 |

Блок пам'яті |

|

0 |

0 |

Блок 0 |

|

0 |

1 |

Блок 1 |

|

1 |

0 |

Блок 2 |

|

1 |

1 |

Блок 3 |

Рисунок 15 – З'єднання контролера динамічної

пам'яті з системною шиною

Контролер формує сигнал ![]() в кінці

циклу читання/запису, що вказує на закінчення циклу взаємодії з центральним

процесором, і сигнал

в кінці

циклу читання/запису, що вказує на закінчення циклу взаємодії з центральним

процесором, і сигнал ![]() на початку

циклу звернення до пам'яті. Використання цих сигналів показане на прикладі

з'єднання контролера i8207 з системною шиною 16-розрядного процесора (рисунок 15).

На виході

на початку

циклу звернення до пам'яті. Використання цих сигналів показане на прикладі

з'єднання контролера i8207 з системною шиною 16-розрядного процесора (рисунок 15).

На виході ![]() формується

сигнал логічного нуля в тому випадку, якщо контролер виконує такти регенерації

інформації в динамічному ОЗП. Сигнал

формується

сигнал логічного нуля в тому випадку, якщо контролер виконує такти регенерації

інформації в динамічному ОЗП. Сигнал ![]() використовується як строб сигнал для управління

шинними формувачами модуля пам'яті. У даному прикладі використані два шинних

формувача К580ВА86 (i8286), оскільки шина даних є 16-розрядною.

використовується як строб сигнал для управління

шинними формувачами модуля пам'яті. У даному прикладі використані два шинних

формувача К580ВА86 (i8286), оскільки шина даних є 16-розрядною.

Таким чином, контролер динамічної пам'яті формує

адресні сигнали, що управляють, в режимах роботи і регенерації, а також

здійснює арбітраж, тобто вирішення конфліктів між запитами на регенерацію і

зверненні до пам'яті. Контролер формує також сигнал готовності блоку

динамічної пам'яті до обміну.

Схема модуля динамічної пам'яті 16-розрядного

процесора показана на рисунку 16.

Рисунок 16 – Система динамічної пам'яті

Динамічна пам'ять організована у вигляді двох

банків, кожен з яких складається з чотирьох блоків ємкістю по 512 Кбайт.

Загальна місткість пам'яті складає 2 Мбайт. Контролер динамічної пам'яті

фактично виконує роль інтерфейсу модуля пам'яті і шини процесора. Шина адреси

процесора з'єднується з контролером. Лінії А1 і А0 підключаються до входів

вибору банку BSO, BS1, біти A3–А11 є адресою рядка, а біти А12–А20 – адресою

стовпця динамічної пам'яті.

7 Динамічні

запам'ятовувальні пристрої підвищеної швидкодії

Сучасні мікропроцесори характеризуються високою

швидкодією. Це вимагає й збільшення швидкості роботи ОЗП, який обмінюються

інформацією із процесорами. Особливо гостро це завдання стоїть перед

розроблювачами динамічних ОЗП, які завдяки максимальній інформаційній ємності й

низької вартості займають провідне місце в складі основної пам'яті комп'ютерів.

Останнім часом запропонований ряд варіантів динамічних

ОЗП підвищеної швидкодії. Методи,

використані в цих ОЗП, засновані на тому, що адреси наступних

звертань до ОЗП найімовірніше розташовані поруч із адресою поточного звертання.

Варіант FPM

Варіант FPM (Fast Page Mode, швидкий сторінковий режим

доступу) ефективний, якщо після звертання до деякому ЗЕ наступне звертання буде

до ЗЕ в тому же рядку.

При читанні по довільній адресі старша напівадреса

вибирає рядок, потім молодша напівадреса вибирає стовпчик у матриці ЗЕ. При

цьому спочатку потрібно перезарядити шину вибірки рядка, а потім шину вибірки

стовпчика, що супроводжується відповідними затримками. При звертанні до рядка

(сторінці), у всіх ЗЕ рядка проходять процеси, що відповідають двом першим

фазам повного циклу обміну (по стробу RAS), і ці елементи готові до виконання чергових

фаз. При звертанні до даних у межах однієї сторінки адреса рядка залишається

незмінним, змінюються тільки адреси стовпців у супроводі сигналу строба CAS.

Поки не змінився номер сторінки, у циклах обміну виключені деякі етапи, що

скорочує тривалість циклів. Характерну

пропорційність часу першого та послідуючих звернень до ЗП можливо записати

наступним чином: 5-3-3-... .

Розроблені ОЗП типу FPM забезпечують час звертання до ЗП

30...40 нс, що допускає їхню роботу із процесорними шинами на тактовій частоті

до 33 Мгц

Структури типу EDORAM

Структури типу EDORAM (Extended Data Out RAM, тобто ОЗП з

розширеним виводом даних) близькі до структур FPM і відрізняються від них

модифікацією процесу виводу даних. В EDORAM дані в підсилювачах-регенераторах

не скидаються по закінченні строба CAS. При цьому на кристалі як би з'являється

статичний регістр, який зберігає рядок. При зверненнях у межах рядка (сторінки)

використовується читання даних з регістра, тобто швидкодіючої статичної

пам'яті. Як і раніше використовується тільки сигнал CAS, але тривалість його

може бути скорочена у порівнянні з режимом FPM. Це збільшує швидкодію ЗП. У

випадку застосування пам'яті типу EDORAM характерна пропорційність часів

звертання буде наступною: 5-2-2-... .

Розроблені EDORAM допускають роботу на частотах до 50

Мгц. Такі ЗП одержали широке поширення, в частковості через тісну наступність

із розробленими раніше ЗП типу FPM, заміна яких на EDORAM вимагає лише

невеликих змін у схемі й синхросигналах ЗП.

Структури типу BEDORAM

У структурі типу BEDORAM (Burst EDORAM, тобто з пакетним

розширеним доступом) мається додатково лічильник адрес стовпчиків. При

звертанні до групи слів (пакету) адреса стовпчика формується звичайним способом

тільки на початку пакетного циклу. Для наступних передач адреси утворяться

швидко за допомогою інкрементування лічильника. Характерна пропорційність часу

першого й наступного звернень 5-1-1-1 (мається на увазі часто застосовуваємий

варіант із довжиною пакета, рівним 4). Пам'ять типу BEDORAM не одержала

широкого поширення через появу сильного конкурента - синхронних DRAM (SDRAM), у

яких не тільки досягається пропорційність часів звернень 5-1-1-1, але й сам час

істотно скорочується.

Структура типу MDRAM

У структурах MDRAM (Multibank DRAM, багатобанкові ОЗП)

пам'ять ділиться на частини (банки). Звертання до банків почергове, чим

виключається очікування перезаряду шин. Поки зчитуються дані з одного банку,

інші мають "перепочинок" на підготовку, після якої з'являється

можливість звертання до них без додаткового очікування. При порушенні

черговості й повторному звертанні до того ж банку виконується повний цикл

звертання до пам'яті. Чим більше банків, тим менше буде повторних послідовних

звернень у той самий банк.

Так як процесор найчастіше зчитує дані по послідовних

адресах, то ефект прискорення роботи ЗП досягається вже при розподілі пам'яті

всього на два блоки, а саме на один з непарними адресами, інший - з парними.

Банки ЗП типу MDRAM можуть будуватися на звичайних DRAM без яких-небудь схемних

змін.

Структури типу SDRAM

Хоча перехід від базової структури DRAM до архітектур FPM

і EDORAM підвищив швидкодію пам'яті, цього виявилося недостатньо для сучасних

комп'ютерів і графічних систем. Пам'ять типу SDRAM (Synchronous DRAM) зайняла

зараз важливе місце як швидкодіюча пам'ять із високою пропускною здатністю.

В SDRAM синхросигнали пам'яті тісно зв'язані з тактовою

частотою системи, у них використається конвеєризація тракту просування

інформації, може застосовуватися багатобанкова структура пам'яті й ін.

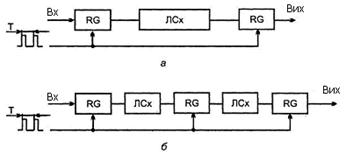

Для більше докладного ознайомлення з пам'яттю типу SDRAM

розглянемо загальне питання про конвеєризації трактів обробки інформації Сутність

конвеєризації полягає в розбивці трактів обробки інформації на ступені. На

рисунку 17 показаний тракт обробки даних, який містить вхідний і вихідний

регістри й логічну схему між ними

Рисунок 17 – Вихідний (а) і

конвеєризований (б) тракти обробки інформації

Застосування конвеєра збільшує потік інформації від входу

до виходу за одиницю часу, хоча, у той же час, одиниця інформації проходить від

входу до виходу за більший час, чим у схемі без конвеєризації.

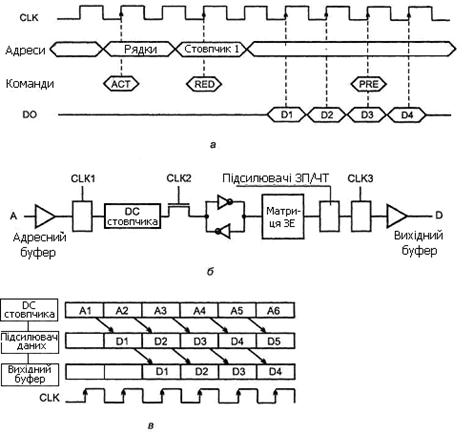

У мікросхемах SDRAM зовнішні керуючі сигнали фіксуються

позитивними фронтами тактових імпульсів і використаються для генерації команд,

які управляють процесами в ЗП. Команда ACT (Active) пов'язана з вибором рядка

по відповідній адресі. Команда RED (Read) визначає адресу першого стовпчика для

читання даних. Команда PRE (Precharge) пов'язана з етапом попереднього заряду

шин.

Перше слово після формування адреси з'являється із

запізнюванням на кілька тактів (Access Latency). Час доступу при цьому

"звичайне", тобто таке, якої б воно було в стандартному ЗП. Адреси

наступних слів формуються внутрішнім лічильником, і слова з'являються в кожному

такті (рисунок 18, а). Щоб прискорити темп появи слів у пакеті,

організується триступінчастий конвеєр (рисунок 18, б). Роботу конвеєра

можна визначити як паралельне функціонування послідовно активізуємих блоків.

Відповідно до керування тактами кожний сегмент схеми стовпчика працює в паралель

із іншими (рисунок 18, в).

Рисунок 18 – Часові діаграми (а), триступінчастий конвеєр

(б) і тимчасові співвідношення обробки інформації (в) для синхронних динамічних

ОЗП

В мікросхемах SDRAM передбачають можливість регулювання

запізнювання першого доступу з метою пристосування пам'яті до частотних вимог

системи й довжини пакета, у якому слова читаються або записуються в кожному

такті після всього однією командою. До переваг SDRAM ставиться відсутність

великих проблем за узгодженням взаємного положення в часі вхідних сигналів, що

в деяких випадках може бути складним. Тут положення полегшується, тому що

вхідні сигнали фіксуються фронтами тактових імпульсів, які жорстко задають моменти їхньої появи й

зникнення. В SDRAM легко реалізуються й багатобанкові системи пам'яті на одному

кристалі.

Структури типу RDRAM

Мікросхеми названі по імені фірми розроблювача — Rambus

(RDRAM — Rambus DRAM). Вони представляють собою байт - послідовну пам'ять із

дуже високим темпом передачі байтів. Основними нововведеннями архітектурного

плану є синхронізація обома фронтами тактових імпульсів і спеціальний

новий інтерфейс Rambus Channel. Синхронізація принципово подібна із

застосовуваної в SDRAM.

У першій розробці при частоті тактових імпульсів 250 МГц

отриманий темп передачі байтів 500 МГц (2 нс/байт). Надалі частота ще

підвищилася в 1,5–3 рази.

Інтерфейс Rambus Channel має всього 13 сигнальних ліній,

що значно менше, ніж у традиційних мікросхем пам'яті. В інтерфейсі немає

спеціалізованих адресних ліній. Замість звичайної адресації по інтерфейсу

посилають пакети, що включають у себе команди й адреси. Спочатку посилається

пакет запитів, на який пам'ять відповідає пакетом підтвердження, після чого йде

пакет даних. Через такий процес перший доступ до даних виявляється сильно

запізнілим. У першій розробці запізнювання становило 128 нс. Тому при читанні

окремих слів RDRAM зовсім неефективна. Середня частота передачі байтів

залежить від довжини пакета даних. При обміні пакетами по 256 байт середня

частота буде 400 Мгц (до 2 нс додається 0,5 нс на байт), при пакетах по 64

байта - 250 Мгц і т.д.

RDRAM ідеально підходить для графічних і мультимедійних

додатків з типовим для них процесом - швидкою видачею довгої послідовності слів

для формування зображення на екрані або подібних із цим завдань.

Структура DRDRAM

Це близький родич RDRAM, який називається Direct RDRAM (DRDRAM). У цьому

різновиді архітектури RDRAM вдосконалений такий фактор, як великий час

запізнювання при першому доступі до даних. Це розширило область використання

DRDRAM. Сьогодні в області швидкодіючих DRAM домінують синхронні (SDRAM). Для

некомп'ютерних застосувань, що вимагають більших ємностей пам'яті, ця ситуація

може зберегтися на багато років У комп'ютерних схемах DRDRAM представляється сильною альтернативою. Маючи час першого

доступу, такі ж як в SDRAM, DRDRAM не деградують по швидкості при довільних

зверненнях більше, ніж звичайні синхронні DRAM. Пропускна ж здатність у них продовжує збільшуватися. Уже є

мікросхеми DRDRAM з 16-розрядним

інтерфейсом (первісні варіанти RDRAM мали

8-розрядні). При роботі на тактовій частоті 400 МГц і схемотехниці DDR (Double

Data Rate), яка передбачає тактування процесів обома фронтами імпульсів, такі

DRDRAM дають пропускну здатність (Bandwidth) усередині пакета 1,6 Гбайт/с.

Структура типу CDRAM

У структурах CDRAM (Cached DRAM, кешована DRAM) на одному

кристалі з DRAM розміщена статична кеш-пам'ять (кеш першого рівня). При цьому

кеш забезпечує швидкий обмін із процесором, якщо інформація перебуває в кеше, а

також швидке відновлення свого вмісту. Остання можливість пов'язана з тим, що

розміщення кеша на одному кристалі з DRAM робить зв'язку між ними внутрішніми

(реалізованими усередині кристала), а в цьому випадку розрядність шин може бути

велика і обмін може проводитись більшими блоками даних. Наприклад, в CDRAM

фірми Ramtron застосована 2048-розрядна шина для відновлення вмісту кеша.

Як синонім позначення CDRAM іноді використається

позначення EDRAM (Enhanced DRAM). Кешування ефективно при виконанні програм,

для яких промахи відносно кеша досить рідкі.