Розділ 3.

Однокристальні

мікроконтролери

Архітектура AVR мікроконтролерів

1 Архітектура AVR мікроконтролерів

2

Паралельні порти введення/виведення

3

Регістр керування мікроконтролером MCUCR та режими

енергозбереження

1 Архітектура

AVR мікроконтролерів

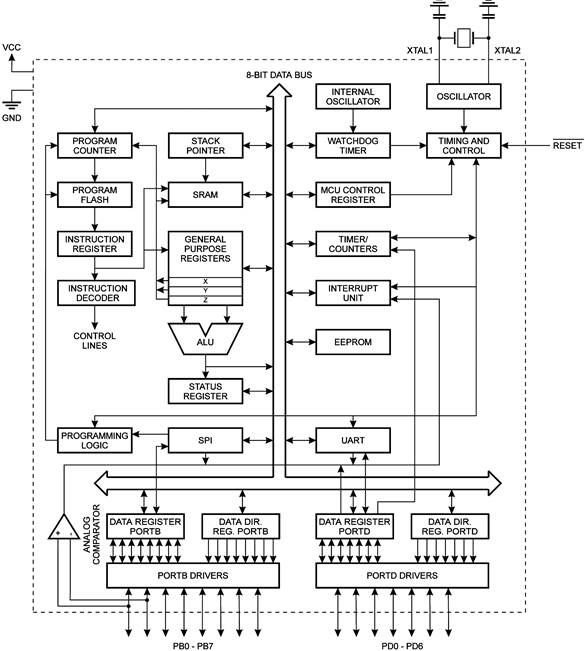

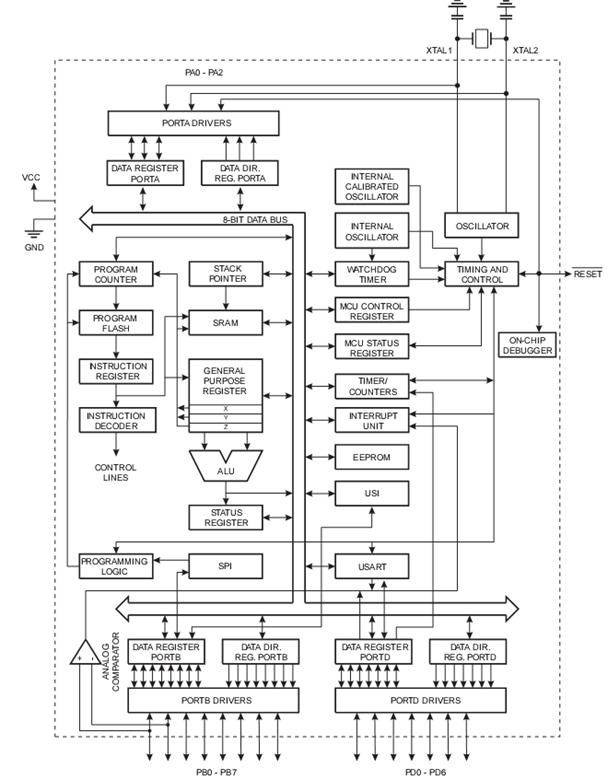

Мікроконтролери сімейства

AVR мають єдину базову структуру. Узагальнена

структурна схема мікроконтролера зображена на рисунку

1.

Рисунок 1 – Струкутрна схема AVR мікроконтролерів

До складу мікроконтролера входять:

- генератор

тактового сигналу (GCK);

- процесор

(CPU);

-

постійний запам'ятовуючий пристрій для збереження

програми виконаний за технологією Flash (FlashROM);

-

оперативний запам'ятовуючий пристрій статичного типу

для збереження даних (SRAM);

-

постійний запам'ятовуючий пристрій для збереження

даних, виконаний за технологією EEPROM, (EEPROM);

-

набір периферійних пристроїв для вводу/виводу даних і

керуючих сигналів, і виконання інших функцій.

До складу

процесора (CPU) входять:

- лічильник

команд (PC);

- арифметико-логічний

пристрій (ALU);

- блок

регістрів загального призначення (GPR, General Purpose Regіsters) і інші

елементи.

Крім регістрів загального призначення в мікроконтролері маються регістри спеціальних функцій, що у

сімействі AVR називаються регістрами введення/виведення (І/O Regіsters,IOR). За участю

цих регістрів здійснюються:

-

керування роботою мікроконтролера

і окремих його пристроїв;

-

визначення стану мікроконтролера

і окремих його пристроїв;

-

ввід даних у мікроконтролер

й окремі його пристрої, виведення даних і виконуються інші функції.

Для нумерації регістрів введення/виведення

використовуються номери від 0 до 63 (від $00 до $3F, де $ - показник

шістнадцятирічного коду). Кожному регістру присвоєне ім'я, пов'язане з функцією, яку виконує цей регістр. Мікроконтролери різних типів мають різний склад регістрів

введення/виведення, при цьому регістри з однаковими номерами можуть мати різні імена.

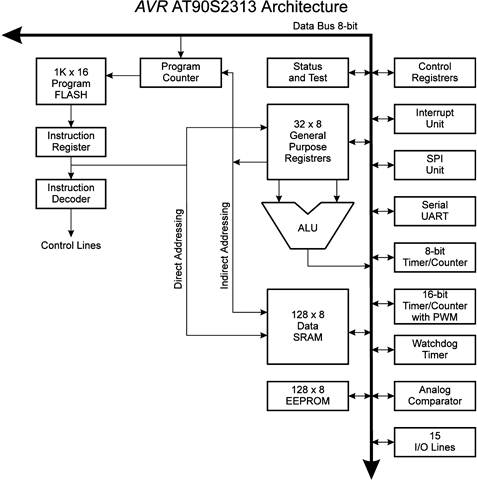

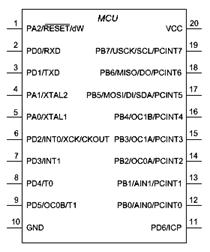

Структурна схема мікроконтролера

AT90S2313 наведена на рисунку 2. Мікроконтролери сімейства

AVR є пристроями синхронного типу. Дії, що виконуються у мікроконтролері, прив'язані до імпульсів

тактового сигналу.

Як

генератор тактового сигналу (GCK) використовується:

-

внутрішній генератор із зовнішнім кварцовим чи

керамічним резонатором (XTAL);

-

внутрішній RC-генератор (ІRC);

-

внутрішній генератор із зовнішнім RC-колом (ERC);

-

зовнішній генератор (ЕХТ).

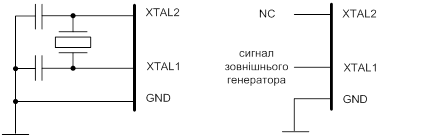

У мікроконтролерів, які

мають внутрішній генератор із зовнішнім резонатором (XTAL), резонатор

підключається до виводів XTAL1 н XTAL2, що через конденсатори малої ємності

(20-30 пФ) з'єднуються із шиною GND. Тактова частота визначається робочою

частотою резонатора. XTAL1 і XTAL2 є входом і виходом, відповідно, який

інвертує підсилювач, що з використанням кварцового чи керамічного резонатора працює як

вбудований генератор, як показано на рис. 3. При використанні зовнішнього

джерела тактової частоти вивід XTAL2 повинний залишитися вільним, сигнал

подається на вивід XTAL1.

Рисунок 2 –

Архітектура мікроконтролера AT90S2313.

Рисунок 3 – Приєднання тактового генератора та зовнішнього джерела тактового

сигналу

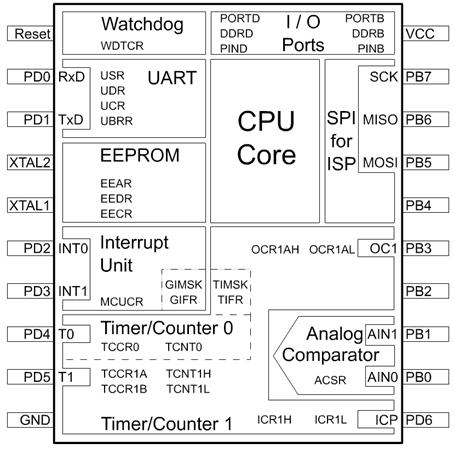

Рисунок 4 – Зовнішній вигляд мікроконтролера

AT90S2313

Таблиця1 –

Призначення виводів мікроконтролера AT90S2313

|

VCC |

Напруга живлення |

|

GND |

Земля |

|

Port B (PB7- PB0) |

8-розрядний двонаправлений порт І/O з вбудованими навантажувальними резисторами. Вихідні

буфери забезпечують струм 20 мА. При

використанні виводів порту як входи й

установці зовнішнім сигналом у низький стан, струм буде випливати тільки при

підключених вбудованих навантажувальних резисторах. Порт B використовується

також при реалізації різних спеціальних функцій. |

|

Port D (PD6-PD0) |

8-розрядний двонаправлений порт І/O з вбудованими навантажувальними резисторами. Вихідні

буфери забезпечують струм 20 мА. При використанні виводів порту

як входи й установці зовнішнім

сигналом у низький стан, струм буде випливати тільки при підключених

вбудованих навантажувальних резисторах. |

|

RESET |

Вхід скидання. Для виконання скидання необхідно утримувати низький рівень

на вході протягом двох машинних

циклів. |

|

XTAL1 |

Вхід підсилювача генератора, що

інвертує, і вхід схеми вбудованого генератора тактової частоти. |

|

XTAL2 |

Вихід підсилювача генератора, що

інвертує. |

Процесор (CPU) формує адресу наступної команди,

вибирає команду з пам'яті й організовує її виконання. Код команди має формат

"слово" (16 біт) або "два слова".

До складу процесора крім лічильника команд (PC),

арифметико-логічного пристрою (ALU) і блоку регістрів загального призначення

(GPR) входять:

·

регістр стану мікроконтролера

SREG;

·

регістр-показник стека SP або SPL і SPH.

ALU з'єднано безпосередньо з усіма 32 швидкодіючими

регістрами загального призначення. Операції ALU підрозділяються на три основні

категорії: арифметичні, логічні й операції над бітами.

Рисунок 5 –

Ядро CPU мікроконтролерів AVR

Рисунок 6 – Струкутрна схема мікроконтролера Attiny2313

Рисунок

7 – Зовнішній

вигляд мікроконтролера ATtiny2313

Таблиця 2 – Функції виводів мікроконтролера Attiny2313

|

Контакт |

Вивід |

Функції |

|

1 |

РА2/RESET/dW |

Лінія

РА2/Вхід скидання/Вивід відладчика |

|

2 |

РD0/RXD |

Лінія РD0/Прийом

даних UART |

|

3 |

РD1/TXD |

Лінія РD1/Передача

даних UART |

|

4 |

PA1/XTAL2 |

Лінія

РА1/Вихід на зовнішній резонатор |

|

5 |

PA0/XTAL1 |

Лінія

РА0/Інвертований вхід для кварцового резонатора, вхід зовнішнього генератора |

|

6 |

РD2/INT0/XCK/CKOUT |

Лінія РD2/Зовнішнє

переривання 0/Передача тактового сигналу USART/Вихід

системного тактового сигналу |

|

7 |

PD3/INT1 |

Лінія PD3/Зовнішнє

переривання 1 |

|

8 |

PD4/T0 |

Лінія PD4/Вхід

зовнішнього тактового сигналу для таймера/лічильника 0 |

|

9 |

РD5/OC0B/T1 |

Лінія PD5/Вихід

сигналу співпадіння в каналі В таймера/лічильника

1/Вхід зовнішнього тактового сигналу для таймера/лічильника 1 |

|

10 |

GND |

Земля |

|

11 |

РD6/ICP |

Лінія РD6/Вхід

захоплення таймера/лічильника 1 |

|

12 |

РB0/AIN0/PCINT0 |

Лінія РB0/Неінвертований вхід аналогового компаратора |

|

13 |

PB1/AIN1/PCINT1 |

Лінія РB1/Інвертований

вхід аналогового компаратора |

|

14 |

PB2/OC0A/ PCINT2 |

Лінія РB2/Вихід

сигналу співпадання в каналі А таймера/лічильника 0 |

|

15 |

PB3/OC1A/PCINT3 |

Лінія PB3/Вихід

сигналу співпадання в каналі А таймера/лічильника 1 |

|

16 |

PB4/OC1B/PCINT4 |

Лінія PB4/Вихід

сигналу співпадіння в каналі А таймера/лічильника 1 |

|

17 |

PB5/MOSI/DI/SDA/PCINT5 |

Лінія PB5/Лінія

вводу даних універсального 3-провідного послідовного інтерфейсу/Лінія даних

2-провідного послідовного інтерфейсу |

|

18 |

PB6/MISO/DO/PCINT6 |

Лінія PB6/Лінія

виводу даних універсального 3-провідного послідовного інтерфейсу |

|

19 |

PB7/USCK/SCL/PCINT7 |

Лінія PB7/Лінія

тактового сигналу універсального 3-провідного послідовного інтерфейсу/Лінія

синхронізації 2-провідного послідовного інтерфейсу |

|

20 |

VCC |

Напруга живлення |

Архітектурні

відмінності ATtiny2313від AT90S2313

-

програмований внутрішній тактовий генератор;

-

18 програмованих

ліній введення/виведення (замість 15;

додались PA0-PA2);

-

чотири канали

ШІМ (PWM) замість 1(додався режим роботи ШІМ для 8 бітного TC0);

-

універсальний

послідовний інтерфейс USI (Universal Serial Interface), який є основним швидкодіючим послідовним

інтерфейсом для роботи в 2-х (I2C) або3-х (IM – шина) провідному

синхронному режимі передачі даних;

-

повнодуплексний USART (замість

UART).

-

спеціальний вхід

debugWIRE для управління вбудованою системою відлагодження;

-

підтримка як зовнішніх,

так і внутрішніх джерел переривань (додались переривання від PCINT7—0);

-

програмована

схема контролю зниження напруги живлення і виявлення короткочасних збоїв у живленні (BOD);

- автоматичне

перепрограмування пам’яті програм

Для

програмування мікроконтролерів

AVR реалізований

SPI

– інтерфейс: MOSI, MISO, SLK Reset, +5 В, Gnd (рисунок 8).

Рисунок 8 – Підключення мікроконтролера до LPT – порта ПК

для програмування через

SPI –

інтерфейс

У групу периферійних

пристроїв мікроконтролера AT90S2313 входять:

-

паралельні порти введення/виведення;

-

послідовний порт SPІ;

-

послідовний порт UART;

-

таймери-лічильники загального призначення;

-

сторожовий таймер;

-

аналоговий компаратор;

-

програмуємий апаратний

модулятор;

-

блок переривань.

2 Паралельні порти введення/виведення

Всі порти введення/виведення мікроконтролера в режимі цифрового вводу-виводу являють

собою двонаправлені порти, в яких кожен із виводів

може працювати як на ввід, так і на вивід інформації.

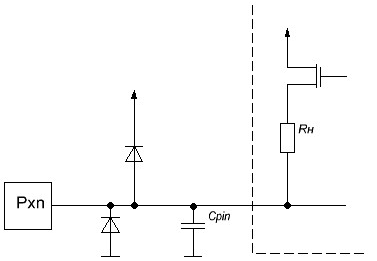

На рисунку 9 зображено

еквівалентну схему вхідних кіл розряду порту введення/виведення. Всі виводи

порту мають індивідуальні резистори навантаження, вхідні схеми кожної лінії

мають по два захисних діоди.

Рисунок

9- Еквівалентна схема вхідних кіл

розряду порту введення/виведення

Для кожного

порту вводу-виводу в МК існує три спеціальних регістри:

-

PORTx – регістр даних;

-

DDRx – регістр керування;

-

PINx – регістр безпосереднього читання стану лінії порту,

де «x» –

назва порту.

Кожен розряд

порту зв’язаний з трьома розрядами спеціальних регістрів:

-

DDxn – розряд номеру n регістра DDRx;

-

PORTxn – розряд номеру n регістра PORTx;

-

PINxn – розряд номеру n регістра PINx.

Біт DDRxn регістру DDRx обирає

напрямок передачі інформації. При DDxn = «1», розряд Рxn працює як вихід, при DDxn = «0» – як вхід.

Якщо розряд

порту настроєно на вхід, то встановлення біту PORTxn в «1» підключить внутрішній навантажувальний

резистор. Для його відключення необхідно в PORTxn записати «0». Одразу після системного скидання всі

виводи всіх портів переходять в третій стан.

Якщо розряд

порту настроєно на вихід, то встановлення біту PORTxn в «1» викличе появу «1» на виході порту. Якщо в

розряд PORTxn записано

«0», то і на виході буде «0».

|

PortD |

$12 |

PortB |

$18 |

PortA |

$1B |

|

DDRD |

$11 |

DDRB |

$17 |

DDRA |

$1A |

|

PinD |

$10 |

PinB |

$16 |

PinA |

$19 |

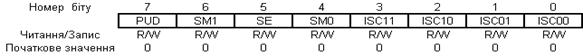

3 Регістр керування мікроконтролером MCUCR та режими енергозбереження

Регістр

керування мікроконтролером (MCUCR – $35) містить біти керування режимами переривань. На

рисунку 10 показано його структуру.

Рисунок 10 - MCUCR

Біти 0,1

(ISC00, ISC01) – режим виклику зовнішнього переривання INT0.

Біти 2,3

(ISC10, ISC11) – режим виклику зовнішнього переривання INT1.

Біти 4,6 (SM0, SM1) – вибір режиму пониженого споживання.

Біт 5 (SE) – дозвіл режиму пониженого споживання.

Біт 7 (PUD) – керування

навантажувальними резисторами (глобальне). Якщо значення біту 1, то

навантажувальні резистори усіх розрядів усіх портів відключені

Біти 6, 4 — SM1...0: Розряди режимів сна. Вони дозволяють вибрати один

з 4

режимів сна (таблиця 3).

Таблиця 3

– Вибір режимів сна

|

SM1 |

SM0 |

Режим сна |

|

0 |

0 |

Режим Idle |

|

0 |

1 |

Режим Power-down |

|

1 |

1 |

Режим Power-down |

|

1 |

0 |

Режим Standby |

Режим

Standby рекомендується вибирати тільки при

використанні зовнішнього кварцового

резонатора.

Біт

5 — SE: Дозвіл режиму сна. Біт SE має

бути встановлений в одиницю для того, щоб по команді SLEEP мікроконтролер

перейшов в сплячий режим. Щоб уникнути випадкового переходу в сплячий режим,

рекомендується встановлювати біт SE в одиничний стан безпосередньо перед

викликом команди SLEEP і скидати його відразу після пробудження.

Режим Idle

Якщо біти SM1 - 0 встановлені в 00, команда SLEEP

примушує мікроконтролер перейти в режим Idle. При цьому центральний процесор зупиняється, інші

пристрої продовжують працювати, а саме:

-

послідовний канал UART;

-

аналоговий компаратор;

-

універсальний послідовний інтерфейс;

-

таймери/лічильники;

-

сторожовий таймер;

-

система переривання.

У режимі Idle відключаються

сигнали CLKCPU, CLK FLASH, а усі інші сигнали залишаються

включеними. Режим Idle дозволяє микроконтролеру

пробудитися як при виникненні зовнішніх переривань, так і внутрішніх, таких як

переповнювання таймера і закінчення передачі по UART.

Якщо пробудження по перериванню від аналогового

компаратора не потрібно, компаратор може бути відключений шляхом скидання

відповідного біта в регістрі стану - ACSR. Це зменшить споживану потужність в

режимі Idle.

Режим Power-down

Коли біти SM10 встановлені в 01 або 11, команда SLEEP

заставляє мікроконтролер перейти в режим Power - down. У цьому режимі

робота зовнішнього генератора припиняється.

В той же час такі зовнішні переривання, як переривання

по каналу USI і переривання по спрацьовуванню сторожового таймера, продовжують

працювати (якщо вони дозволені). Вихід МК з такого сплячого стану можливий за

наступних умов:

- системне скидання від зовнішнього сигналу;

- скидання при спрацьовуванні охоронного таймера;

- скидання при короткочасному зниженні напруги живлення;

- переривання від каналу USI;

- зовнішнє переривання INT0;

- переривання при зміні стану будь-якого виводу.

У режимі Power - down відключаються усі основні внутрішні синхросигнали, а залишаються активними лише ті пристрої,

які працюють в асинхронному режимі.

При пробудженні з режиму Power

- down умова, що викликала пробудження, має бути

присутньою до тих пір, поки процес пробудження не закінчиться. В процесі пробудження

тактовий генератор повинен вийти із загальмованого стану, запуститися і увійти

до стійкого режиму роботи.

Режим Standby

Якщо біти SM10 встановлені в 10 і при цьому

використовується зовнішній кварцевий резонатор, то з

появою команди SLEEP мікроконтролер переходить в

сплячий режим Standby. Цей режим ідентичний режиму Power - down за винятком того, що

системний генератор продовжує працювати. З режиму Standby

микроконтроллер пробуджується всього за шість циклів

тактового сигналу.

Активність різних внутрішніх синхросигналів

і джерела пробудження в різних режимах енергозбереження наведені в таблиці 4.

Таблиця 4 – Активність

сигналів та джерела пробудження в різних режимах енергозбереження

|

Режим |

Активність

сигналів |

Генератор |

Джерела пробудження |

|||||

|

CLKCPU |

CLK FLASH |

CLK IO |

Включений |

INTO,

1NT1 та зміни на будь-якому виводі |

Готовність до старту USI |

Готовність SPM/ EEPROM |

Інші пристрої I/O |

|

|

Idle |

|

|

X |

X |

X |

X |

X |

X |

|

Power -down |

|

|

|

|

X |

X |

|

|

|

Standby |

|

|

|

X |

X |

X |

|

|

Мікросхема

ATtiny2313 має чотири джерела сигналу скидання:

- скидання

при включенні живлення, який відбувається у тому випадку, якщо напруга живлення

виявиться нижче за пороговий рівень для цього режиму

(VPOT);

- зовнішнє

скидання, яке відбувається у тому випадку, якщо на вхід RESET поступає сигнал

низького логічного рівня тривалістю не менше одного такту системного

генератора;

- скидання

від сторожового таймера, яке відбувається в трьох випадках:

1)

якщо витік період роботи сторожового таймера;

2) якщо сторожовий таймер

включений;

3)

якщо заборонено переривання по сторожовому таймеру;

- скидання

при зниженні живлення, яке відбувається, якщо напруга живлення виявиться нижче

за пороговий рівень для цього режиму (VBOT), а

система контролю рівня живлення включена.

Регістр

статусу системи скидання містить інформацію про те, яке з джерел сигналу

скидання викликало останній перезапуск системи

|

Біти |

|

|

||||||||

|

|

|

MCUSR |

||||||||

|

Читання/Запис |

|

|

||||||||

|

Початковий стан |

|

|

Рисунок 11 – Регістр статусу системи скидання - MCUSR

Біт

3 - WDRF: прапор скидання від сторожового

таймера. Цей біт встановлюється в 1,

якщо сталося скидання при спрацьовуванні сторожового таймера. Біт скидається

після скидання по включенню живлення або після примусового запису логічного

нуля.

Біт

2 - BORF: Прапор скидання при зниженні живлення.

Цей біт встановлюється в 1, якщо сталося скидання при короткочасному зниженні

напруги живлення (спрацьовуванні схеми BOD). Біт скидається після скидання по

включенню живлення або після примусового запису логічного нуля.

Біт

1 - EXTRF: Прапор зовнішнього скидання. Цей біт

встановлюється в одиницю, якщо сталося зовнішнє скидання. Біт скидається після

скидання по включенню живлення або після примусового запису логічного нуля.

Біт

0 - PORF: Прапор скидання по включенні живлення.

Цей біт встановлюється в одиницю, якщо сталося скидання по включенні живлення.

Біт скидається тільки при примусовому запису логічного нуля.